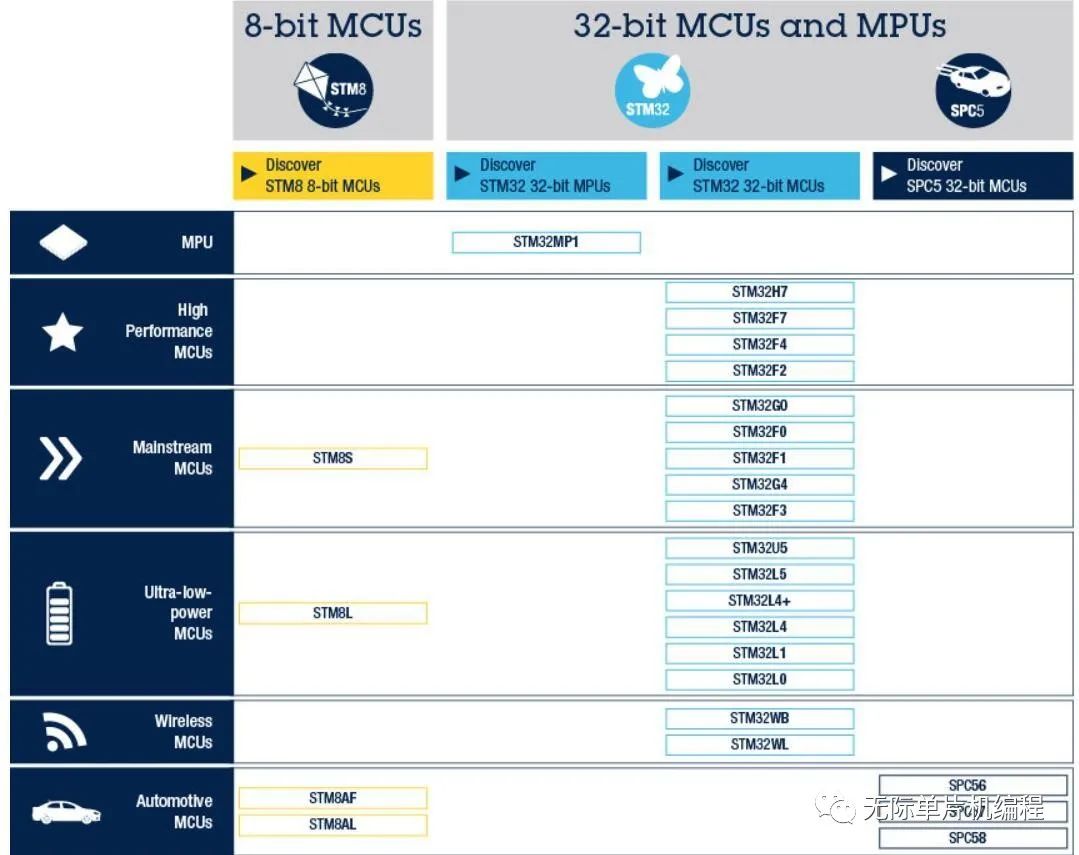

下文将介绍STM32F207的时钟系统如何将25M晶振时钟转换为120M系统主频时钟的。

01、时钟系统介绍

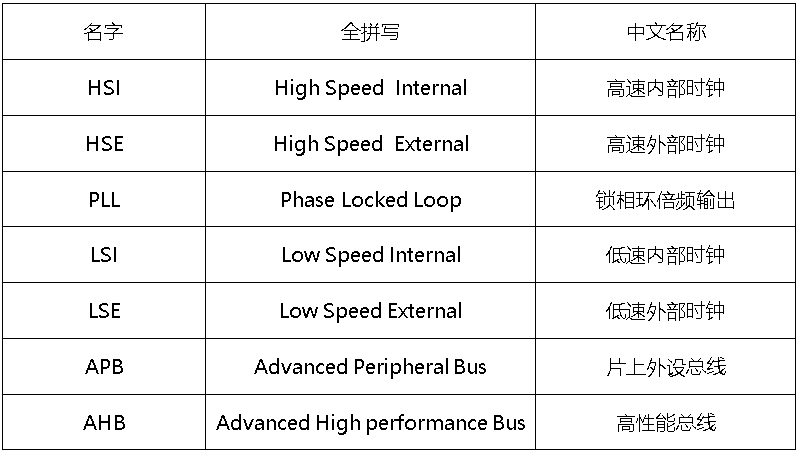

▲时钟系统专业名词缩写

时钟系统关键组成部分

01、内部高速时钟(HSI)

HSI时钟信号可以通过内部16MHZ的RC振荡器产生,可以直接用于系统时钟或者用于PLL输入。

HSI的RC振荡器的优势是:在最小成本(没有外部器件)情况下提供一个时钟源。它的启动速度要比HSE晶体振荡器更快,但是即使校准频率后,它的精度仍然小于外部晶体振荡器或陶瓷谐振器。

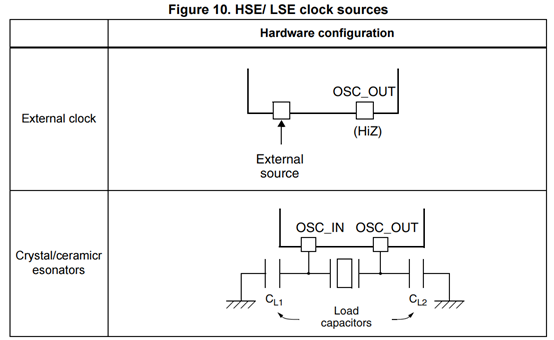

02、外部高速时钟(HSE)

外部高速时钟信息(HSE)可以通过两个时钟源产生:

① 外部晶体/陶瓷谐振器

② 外部用户时钟

▲两种时钟源接入示意图

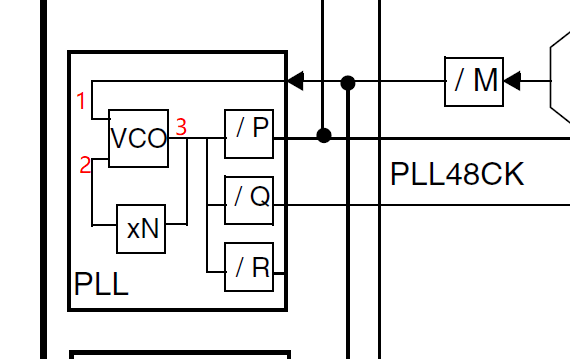

03、主锁相环时钟(PLL)

STM32F2xx具有两个PLL

① 主要的PLL通过HSE或HSI提供时钟,并且有两个输出时钟;

② 专用的PLL(PLLI2S)被用于产生一个精确的时钟去实现高质量音频效果在I2S接口;

HSE/M*N/P得到PLL时钟

关于PLL锁相环说明

从1处输入,3处输出是1的N倍。

3处除以N又作为输入,当1和2的频率一样,就锁定了。(之所以图上是xN,因为从2看向3的)

04、低速外部时钟(LSE)

LSE是一个32.768KHZ低速外部晶振或陶瓷谐振器。

它的优点:提供低速但是高精度时钟给RTC外设,为时钟/日历或其他时间应用。

05、低速内部时钟(LSI)

LSI RC作为一个低速时钟源,它可以运行在停止和待机模式中给独立看门狗(IWDG)和自动唤醒(AWU)。它的时钟频率在32MHZ左右。

02、代码分析

时钟初始化代码在system_stm32f2xx.c文件中,大部分时候我们不需要修改时钟代码的,各个总线的频率我们可以在文件头看到

============================================================================= *============================================================================= * Supported STM32F2xx device revision | Rev B and Y *----------------------------------------------------------------------------- * System Clock source | PLL (HSE) *----------------------------------------------------------------------------- * SYSCLK(Hz) | 120000000 *----------------------------------------------------------------------------- * HCLK(Hz) | 120000000 *----------------------------------------------------------------------------- * AHB Prescaler | 1 *----------------------------------------------------------------------------- * APB1 Prescaler | 4 *----------------------------------------------------------------------------- * APB2 Prescaler | 2 *----------------------------------------------------------------------------- * HSE Frequency(Hz) | 25000000 *----------------------------------------------------------------------------- * PLL_M | 25 *----------------------------------------------------------------------------- * PLL_N | 240 *----------------------------------------------------------------------------- * PLL_P | 2 *----------------------------------------------------------------------------- * PLL_Q | 5 *----------------------------------------------------------------------------- * PLLI2S_N | NA *----------------------------------------------------------------------------- * PLLI2S_R | NA *----------------------------------------------------------------------------- * I2S input clock | NA *----------------------------------------------------------------------------- * VDD(V) | 3.3 *----------------------------------------------------------------------------- * Flash Latency(WS) | 3 *----------------------------------------------------------------------------- * Prefetch Buffer | ON *----------------------------------------------------------------------------- * Instruction cache | ON *----------------------------------------------------------------------------- * Data cache | ON *----------------------------------------------------------------------------- * Require 48MHz for USB OTG FS, | Enabled * SDIO and RNG clock | *----------------------------------------------------------------------------- *============================================================================= ******************************************************************************

在文件开始定义的有系统时钟频率的全局变量SystemCoreClock,其他地方需要时钟频率,可以直接使用该变量。

uint32_t SystemCoreClock = 120000000;

时钟配置从SystemInit函数执行,调用SystemInit的在汇编文件中startup_stm32f2xx.s(Keil编译环境)。

IMPORT __main LDR R0, =SystemInit BLX R0 LDR R0, =__main BX R0 ENDP

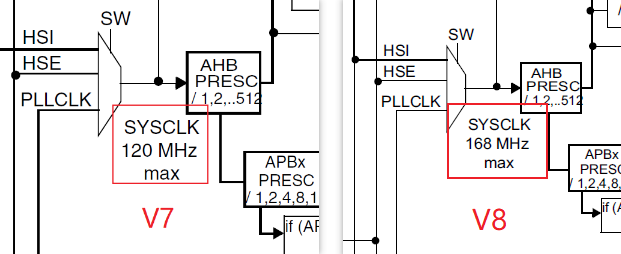

在这里说明一下文档版本的问题:

▲STM32F20X_User_manual的V7版和V8版对比图

上述两图的区别是系统最大时钟从120MHZ变成了168MHZ,我的理解是同样是STM32F20X,ST由于技术进步或其他,使得新版STM32F207芯片超频支持168MHZ。

文档下载地址:

https://www.st.com/en/microcontrollers-microprocessors/stm32f2x7.html#resource

(提示:公众号不支持外链接,请复制链接到浏览器下载)

在线预览地址:

https://www.st.com/content/ccc/resource/technical/document/reference_manual/51/f7/f3/06/cd/b6/46/ec/CD00225773.pdf/files/CD00225773.pdf/jcr:content/translations/en.CD00225773.pdf

(提示:公众号不支持外链接,请复制链接到浏览器下载)

下面我们主要分析SystemCoreClock的120M时钟怎么从一个外部25MHZ的HSE得到的。

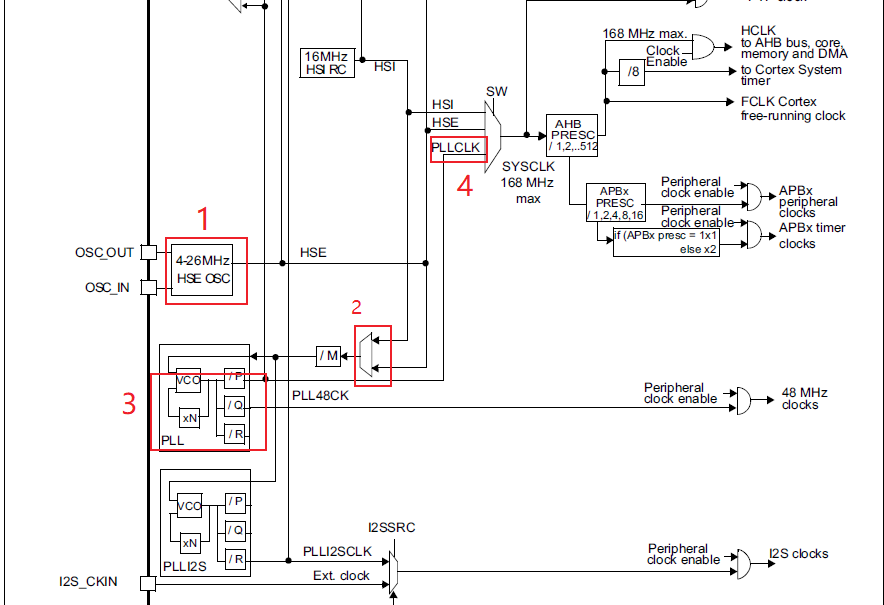

我们要从25MHZ的外部时钟得到120M的系统时钟,需要上图中标注的重要4点:

1、使能HSE

2、选择HSE作为主PLL的输入时钟

3、主PLL倍频后得到120MHZ时钟

4、系统时钟选择主PLL时钟输出作为系统时钟

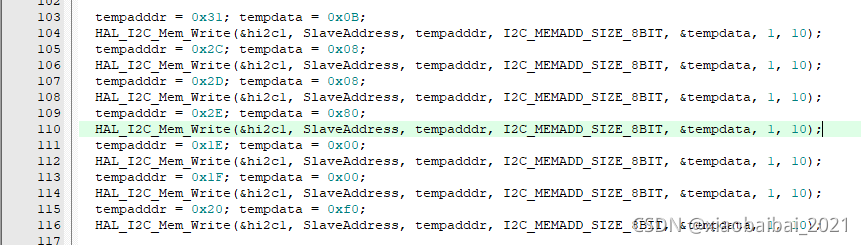

我们找到对应的代码

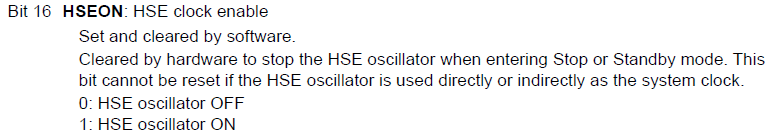

1、使能HSE

/* Enable HSE */ RCC->CR |= ((uint32_t)RCC_CR_HSEON);

在RCC_CR寄存器(RCCclock control register RCC时钟控制器)中,有打开HSE的控制位

2、选择HSE作为主PLL的输入时钟

2、选择HSE作为主PLL的输入时钟

/* Configure the main PLL */RCC->PLLCFGR = PLL_M | (PLL_N 6)

| (((PLL_P >> 1) -1) 16) |

(RCC_PLLCFGR_PLLSRC_HSE) | (PLL_Q 24);

RCC_PLLCFGR_PLLSRC_HSE就是配置HSE作为主PLL的输入时钟

3、主PLL倍频后得到120MHZ时钟

/* Configure the main PLL */RCC->PLLCFGR = PLL_M | (PLL_N 6)

| (((PLL_P >> 1) -1) 16) |

(RCC_PLLCFGR_PLLSRC_HSE) | (PLL_Q 24);

4、配置主PLL作为系统时钟的输入时钟

/* Select the main PLL as system clock source */RCC->CFGR

扫码关注

扫码关注