串音干扰是高速PCB设计的首要解决问题之一,为减少PCB板上的串音问题,很多工程师都会提前分析设计电路,但部分工程师可能不太清楚,PCB板的分层也是串音控制重要因素之一,接下来我们来看看!

在PCB设计时不重视分层,在高速PCB设计是属于重大失误,这是因为分层不但影响传输线的性能,,如:阻抗、延迟和耦合等。而且电路工作容易市场,甚至改变。

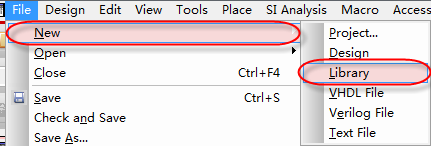

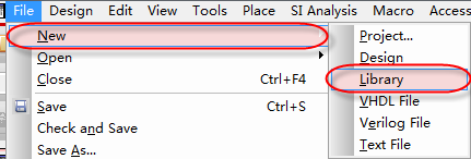

另外一个容易忽略的因素是层的选择,很多时候,前向串音是微带电路中的主要串音干扰,但若设计合理,布线层位于两个电源层之间,这样就很好平衡了容性耦合和感性耦合,具有较低幅值的后向串音便成为主要因素,所以仿真时必须要注意是哪种串音干扰占据主要地位。

布线和芯片的位置关系对串音也有影响,因为后向串音到达接受芯片后反射到驱动芯片,所以驱动芯片的位置性能是非常重要的,因为拓扑结构的复杂性,反射及其他因素,所以很难解释串音主要是受谁影响,如果有多种脱贫结构供选择,最好通过仿真来确定那种结构对串音影响最小。

一个可能减少串音的非几何因素是驱动芯片本身的技术指标,一般原则是选择切换时间长的驱动芯片,以减少串音干扰(解决很多其他由于高速引起的问题也是如此),即使串音不严格地和切换时间成正比,降低切换时间仍然会产生重大影响,许多时候,你对驱动芯片技术无法选择,你只能改变几何参量来达到目的。

扫码关注

扫码关注