- 全部

- 默认排序

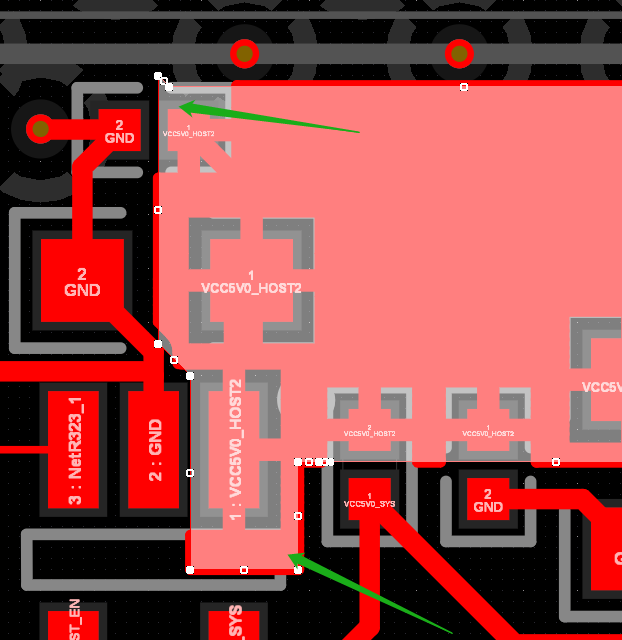

机壳地以及电源地没有正片铺铜处理也没有负片分割处理,注意地是需要处理的:变压器上除了差分信号,其他的加粗20MIL走线:电源层也并未处理电源 :TX RX信号之间用GND走线隔开:RX TX没有创建等长组进行等长:差分对内等长误差为5MIL

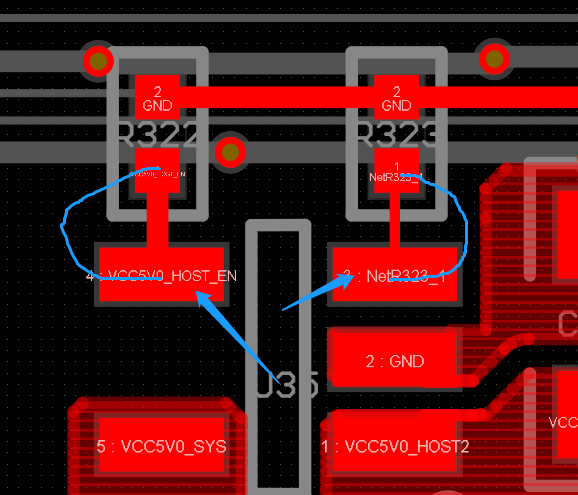

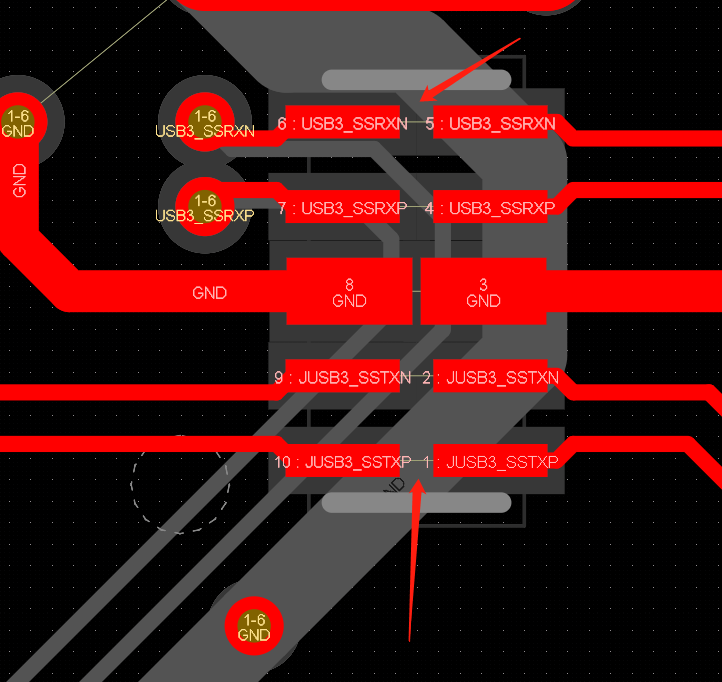

焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊2.差分线处理不当,锯齿状等长不能超过线距的两倍3.差分对内等长误差5mil4.此处需要经过ESD器件在到USB座子5.地网络直接就近打孔即可以上评审报告来源于凡亿教育90天高

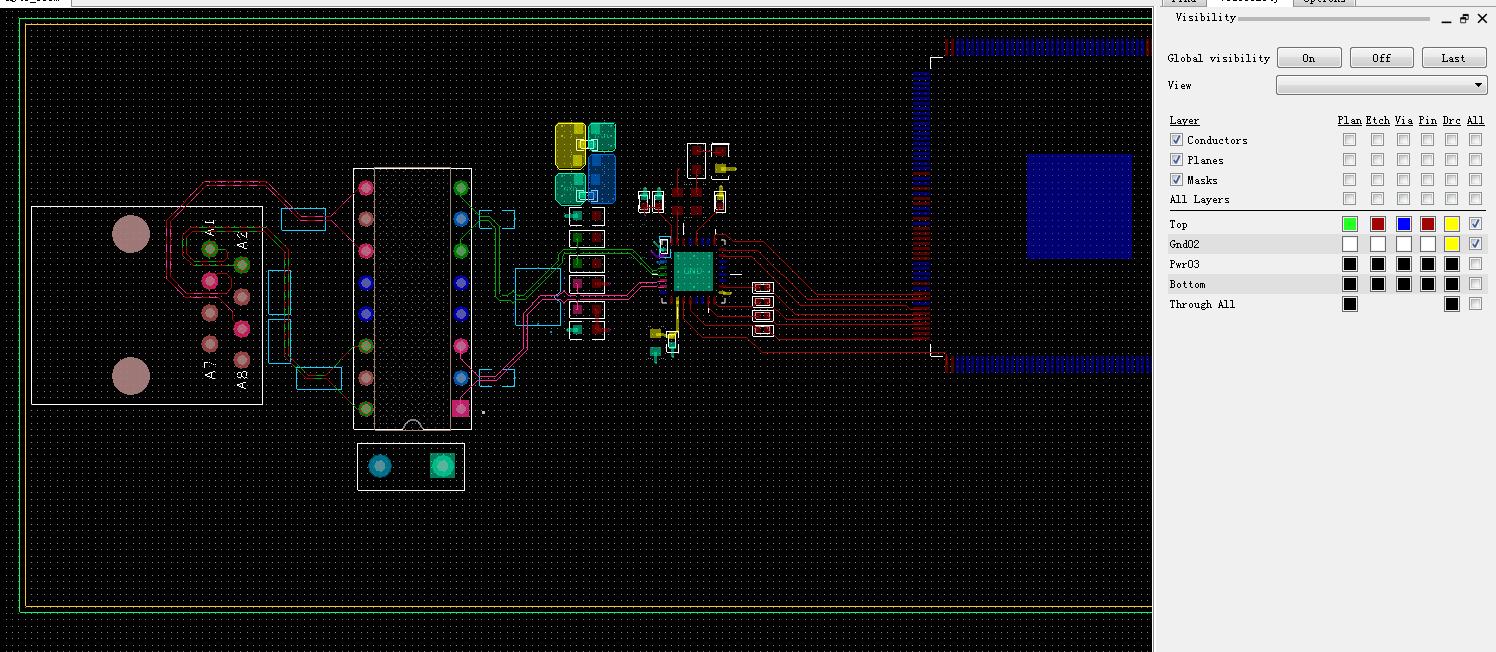

PCB元件布局思路分析

1、首先,我们会对结构有要求的器件进行摆放,摆放的时候根据导入的结构,连接器得注意1脚的摆放位置。 2、布局时要注意结构中的限高要求。 3、 如果要布局美观,一般按元件外框或者中线坐标来定位(居中对齐)。 4、 整体布局要考虑散热。 5、 布局的时候需要考虑好布线通道评估、考虑好等长需要的空间。 6、 布局时需要考虑好电源流向,评估好电源通道。 7、 高速、中速、低速电路要分开。

USB3.0:铺铜不要出现直角以及尖角,需要钝角,都修改下:差分没有耦合走线,重新走线:差分打孔不符合规范,重新扇孔下:走线没连接的删除掉:差分都没有注意耦合走线,都要检查修改:都没有耦合不符合规范。差分对内等长误差为5MIL:自己修改以上

此处存在开路2.差分换层打孔尽量对齐,走线尽量耦合3.差分对内等长不规范,锯齿状等长不超过线距的两倍4.tpye-c差分对内等长误差5mil5.此处走线需要优化一下6.器件摆放尽量中心对齐7.过孔需要盖油处理以上评审报告来源于凡亿教育90天

传输速度越快,误差要求越小?DDR2的数据线等长误差范围为±25mil,那DDR3的数据线等长误差范围是多少呢?

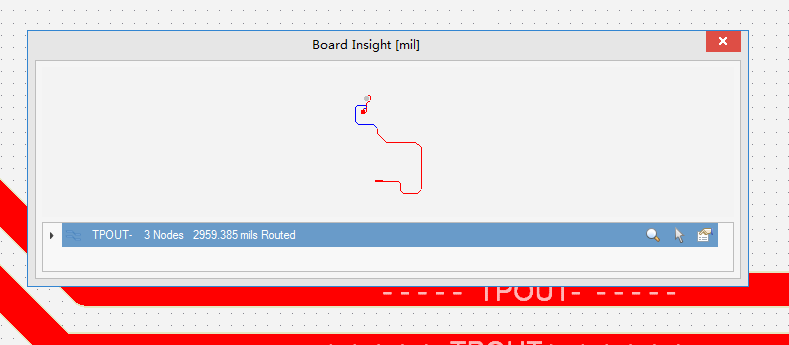

老师您好!我添加差分对的时候多添加了一对,D+C快捷键进入Class,可以查看,但是不能操作,请问怎么删除掉多余的差分对呢?此PCB没有原理图,是手动添加的差分对,方便一起走线和等长;

扫码关注

扫码关注