- 全部

- 默认排序

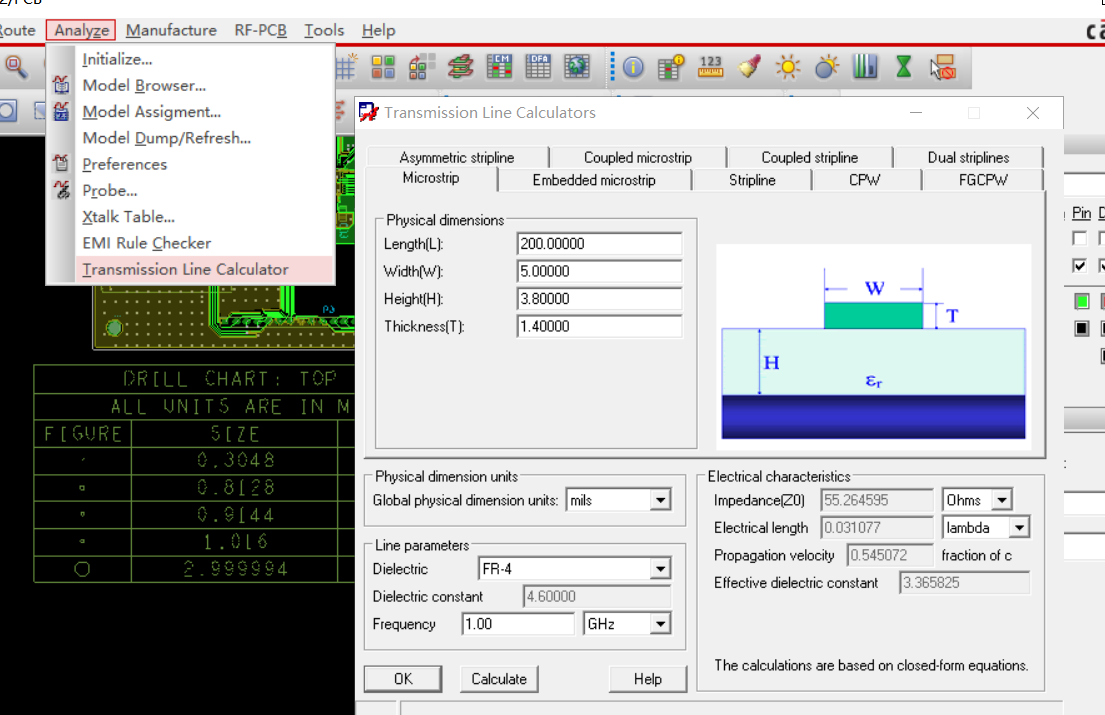

随着信号速率越来越高,PCB设计时,越来越多的数字电路 需要对走线阻抗控制、延迟等传输参数进行计算。Allegro16.6版本提供了一个内置的传输线参数计算工具,能对微带线、嵌入式微带线、带状线、差分线等多种传输数据结构进行传输参数计算。

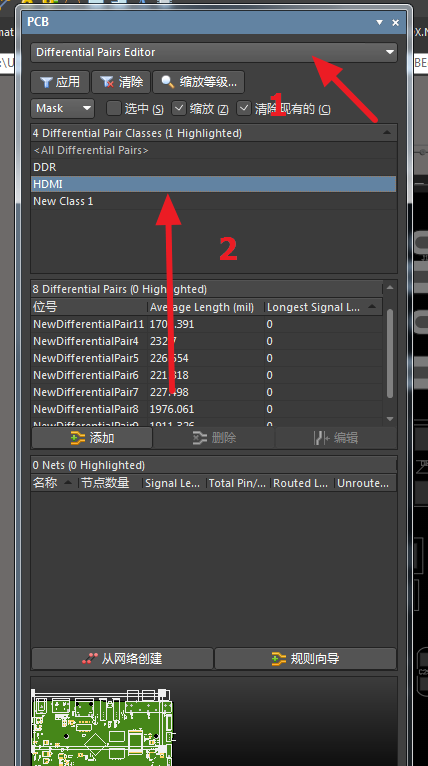

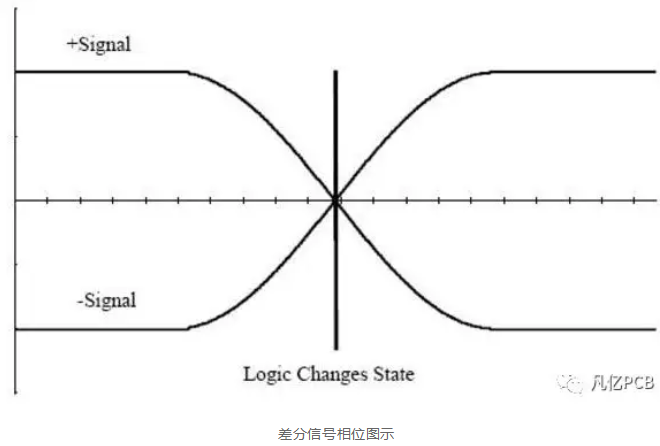

在进行PCB设计的时候,会用到差分,那么首先的第一步就是创建差分,创建完的第二步就是对于刚刚创建的差分进行规则的设置了。在PCB中差分规则是如何设置的呢?其方法又有哪一些呢?

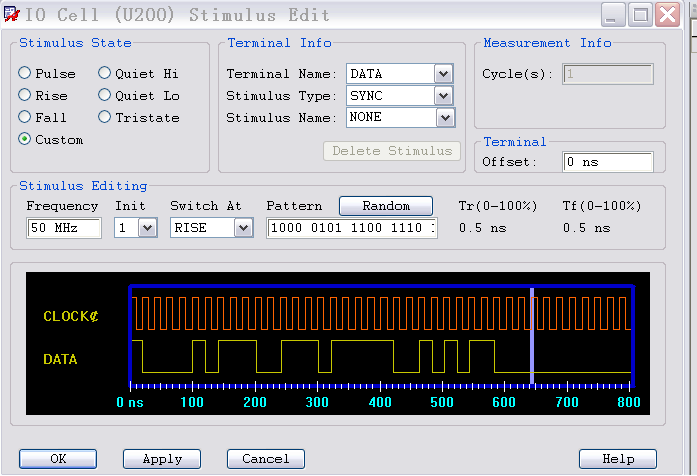

SI分析的前期准备完成之后,就可以进行信号完整性分析了,执行Analyze/SI EMI Sim/Probe命令,然后选择需要进行SI分析的网络或者差分对(模型分配中必须设置好差分对),如下图所示:

为了尽量减小单板设计的串扰问题,PCB设计完成之后一般要对线间距3W规则进行一次规则检查。一般的处理方法是直接设置线与线的间距规则,但是这种方法的一个弊端是差分线间距(间距设置大小不满足3W规则的设置)也会DRC报错,产生很多DRC报告,难以分辨

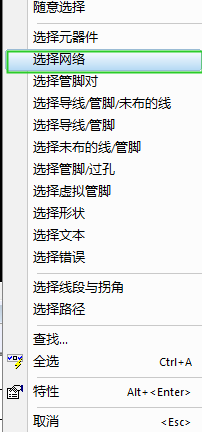

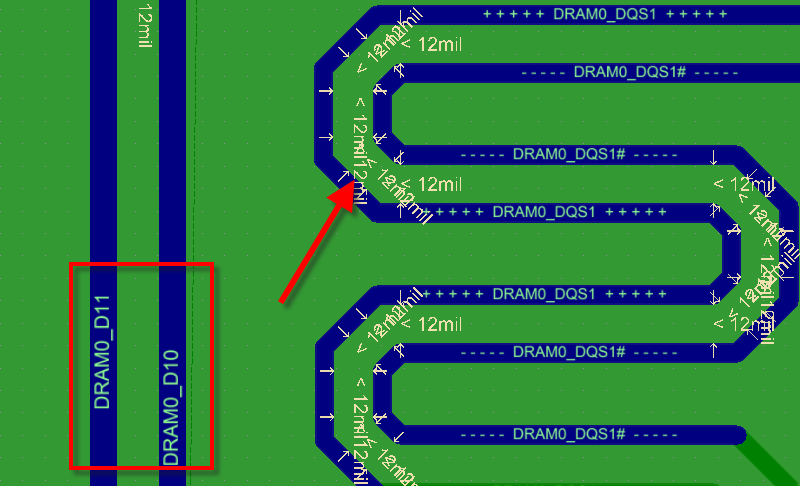

PCB设计:检查线间距时差分间距报错的处理方法 为了尽量减小单板设计的串扰问题,PCB设计完成之后一般要对线间距3W规则进行一次规则检查。一般的处理方法是直接设置线与线的间距规则,但是这种方法的一个弊端是差分线间距(间距设置大小不满足3W规则的设置)也会DRC报错,产生很多DRC报告,难以分辨,如图12-23所示。

前期为了满足各项设计的要求,我们会设置很多约束规则,当一个PCB单板设计完成之后,通常要进行DRC(Design Rule Check)检查。DRC检查就是检查设计是否满足所设置的规则。一个完整的PCB设计必须经过各项电气规则检查。常见的检查项包括间距、开路以及短路的检查,更加严格的还有差分对、阻抗线等检查。

模拟电路电路设计的九个阶段,类似下围棋的段位。从一段到九段都看完后,就掌握自身是哪一个时期的水平了。不容错过哦。 一开始步入这一行,对PMOS/NMOS/BJT那些的只不过是有一个大概的掌握,各类元器件的性能都不太清晰,实际电路设计成哪样的电路也没有想法,路原理图主要是看国内杂志期刊上的文章,或是依照教材上现成的电路,总感觉他们说得都是有道理。做的电路主要是是小规模的模块,做些差分运放,或是带隙基准的仿真那些的就计算着发文章,生怕到时候论文凑不够。总的来说,基本上看见运放还是发怵。感觉spic

扫码关注

扫码关注