- 全部

- 默认排序

PCB压合的原理和流程

为什么常规阻抗控制只能是10%的偏差?不少的朋友非常希望阻抗能控制到5%,甚至我还听说过2.5%的阻抗要求。其实,阻抗控制常规是10%偏差,稍微严格一点的,能做到8%,有很多方面的原因:1、 板材来料本身的偏差2、 PCB加工过程的蚀刻偏差

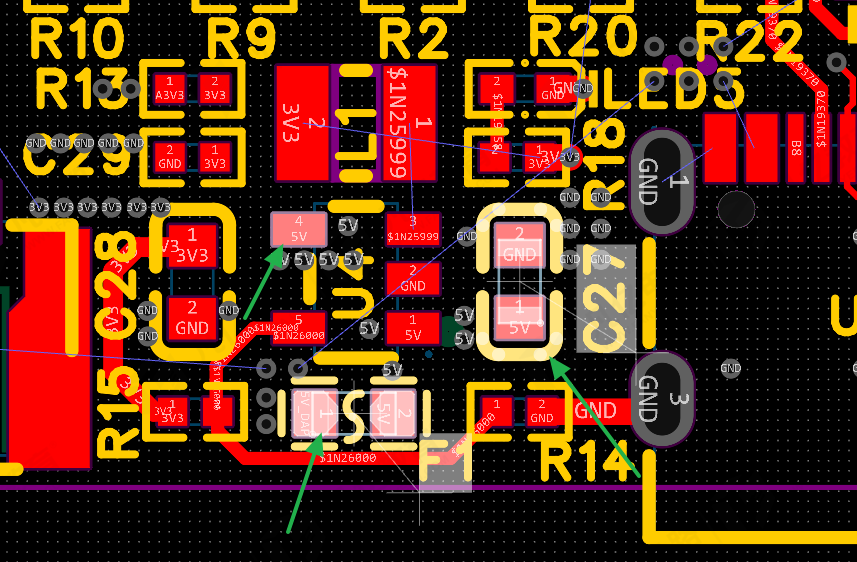

电源输入电容应该靠近管脚放置输出电容电阻应该靠近管脚放置到电感后面输出3.3v晶振布局错误,晶振的一对线要走成类差分的形式, 线尽量短如下图。typec的LCD_R4、LCD_R5要走差分阻抗控制90欧姆做对内等长,差分走线尽量减少打孔换层

答:随着信号传送速度迅猛的提高和高频电路的广泛应用,对印刷电路板也提出了更高的要求。印刷电路板提供的电路性能必须能够使信号在传输过程中不发生反射现象,信号保持完整,降低传输损耗,起到匹配阻抗的作用

在电子工程中,阻抗控制的设定值经常是10%,虽然大家都说这是基于一系列工程和技术上的考量,但也有很多人好奇,为什么阻抗控制不能是其他数值,必须是10%?首先,这就必须要了解阻抗控制的重要性。阻抗控制的目的是确保信号在传输过程中的稳定性和效率

在电子工程中,阻抗控制的设定值经常是10%,虽然大家都说这是基于一系列工程和技术上的考量,但也有很多人好奇,为什么阻抗控制不能是其他数值,必须是10%?首先,这就必须要了解阻抗控制的重要性。阻抗控制的目的是确保信号在传输过程中的稳定性和效率

在高速数据传输中,PCI Express(PCIe)总线标准以其优越的传输性能,成为了计算机及外部设备之间连接的重要桥梁。而在PCIe系统设计中,阻抗控制直接影响着信号完整性和系统稳定性,必须做好阻抗控制,那么应该选择几欧姆?首先,需要了解

在设计PCB时,经常会遇到高速差分线,比如USB、HDMI、LVDS、以太网等等,高速差分线不仅要求信号线的正端和负端信号线宽及线间距保持一致,还需要对差分信号线进行阻抗控制。控制差分信号线的阻抗,对高速数字信号的完整性是非常重要的,因为差分阻抗影响差分信号的眼图、信号带宽、信号抖动和信号线上的干扰

扫码关注

扫码关注