- 全部

- 默认排序

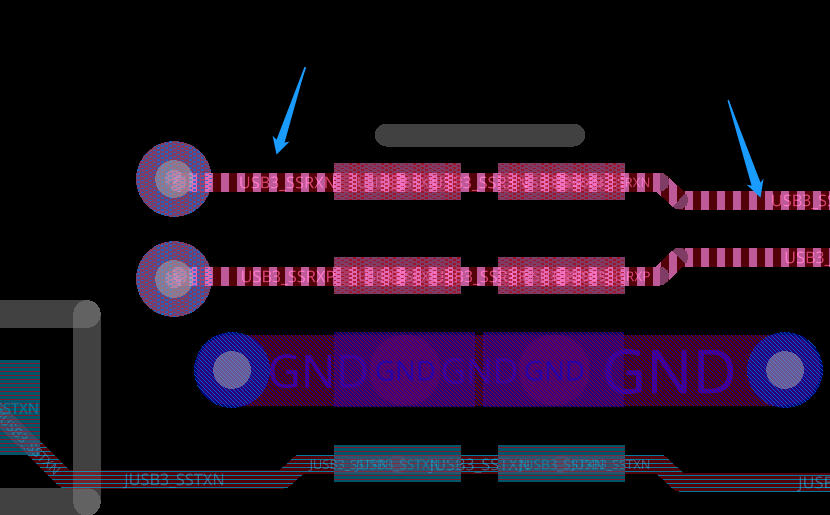

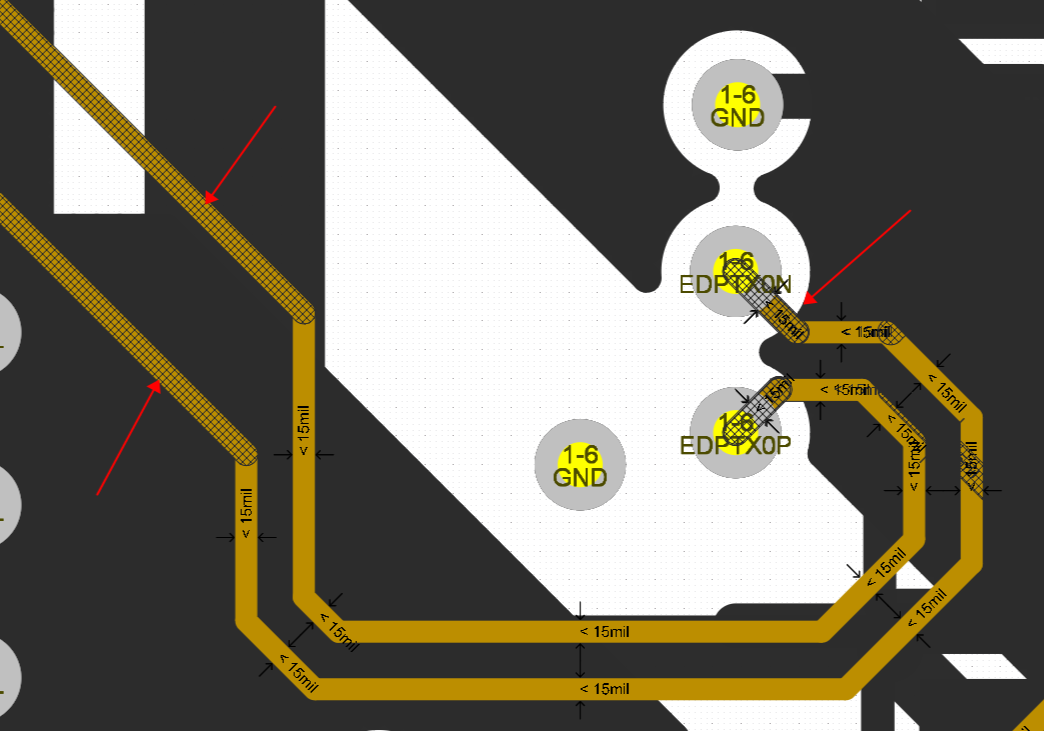

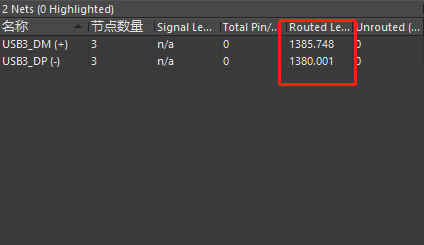

布局没什么问题。拉出焊盘之后注意差分走线保持耦合,重新走下:差分打孔换层两侧打上地过孔,缩短回流路径:建议差分每组直接走GND线包地处理:差分从过孔拉出注意耦合, 连接处重新走下:差分组组内等长误差没什么问题了。以上评审报告来源于凡亿教育9

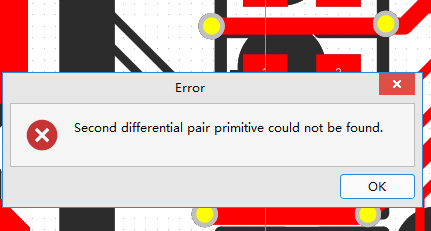

AD差分走线时出现Second differential pair primitive could not be found报错

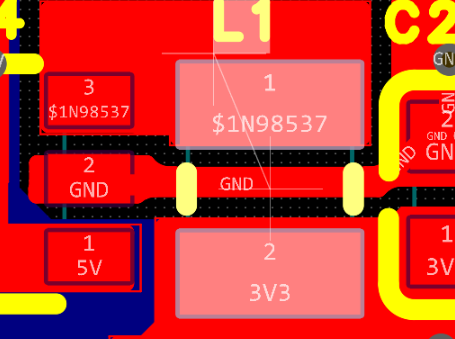

差分走线,信号换层过孔数量,等长长度把控,阻抗控制要求,跨分割的损耗,走线拐角的位置形状,绕线方式对应的插损和回损,布局不妥当造成的一系列串扰和叠层串扰,布局不恰当操作焊盘存在的stub。

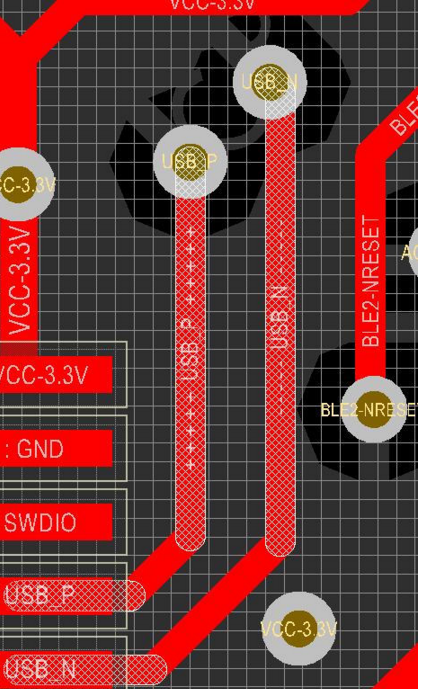

Altium Designer走差分线出现网格是什么原因?答:如图1所示,在AD软件中走差分线出现网格主要是差分线的未耦合长度没有满足差分规则所导致的,未耦合长度指的是差分线中不满足差分间距的长度。图 1 差分走线出现网格走线当出现这种错误

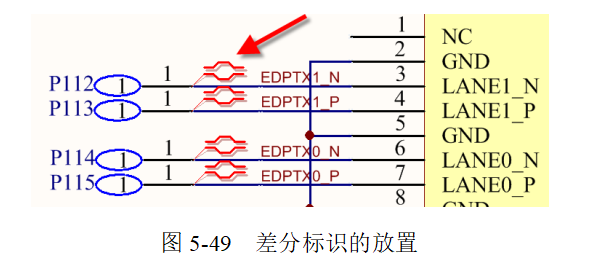

电子设计当中,经常用到差分走线,如USB的D+与D-差分信号、HDMI的数据差分与时钟差分等。那么,如何在原理图中添加差分标识呢?(1)在原理图中,将要设置的差分对的网络名称的前缀取相同的名称,在前缀后面分别加“+”和“-”或者“_P”和“

差分对内误差需要控制在+-5mil这组差分上面没包地差分走线的时候要保持差分间距整版铺一下铜以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.

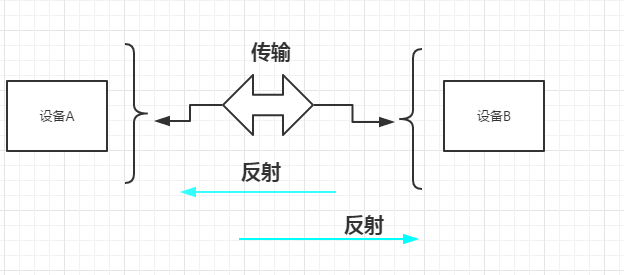

在PCB设计中,电子工程师都知道差分走线必须是等长、等宽、紧密凑近、且在同一层面的两根线,以此降低阻抗变化,但在设计时,许多工程师常常陷入一些误区,本文将针对其中三大常见误区进行解析,希望对小伙伴们有所帮助。误区一:保持等间距比匹配线长更重

扫码关注

扫码关注