- 全部

- 默认排序

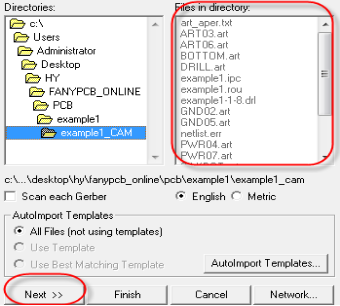

答:第一步,打开Cam350软件,点击File-Import-AutoImport选项,如图6-322所示;

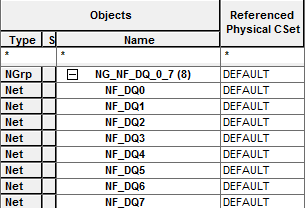

答:在16.6及以上的版本中已经没有Bus总线了,如果需要添加的话,需要添加Net Group,可实现的功能和Bus总线是一样的。

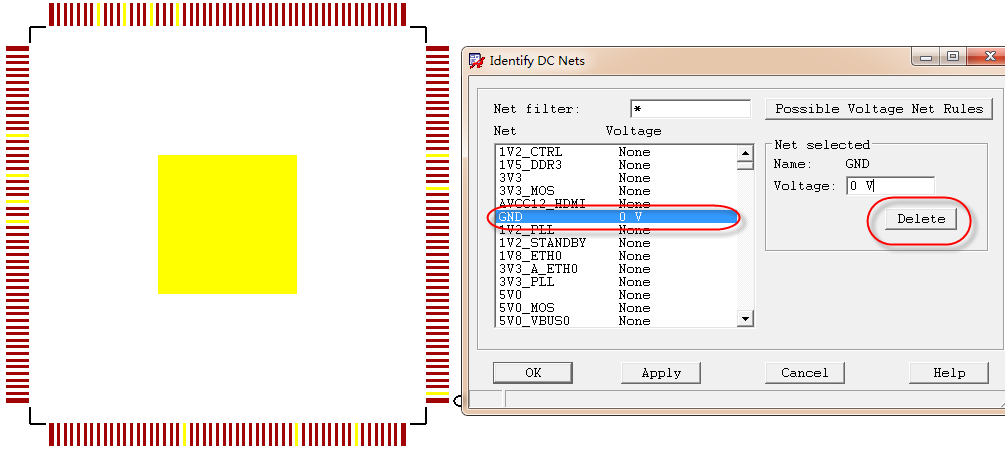

答:我们在PCB设计过程中,一把布线的顺序是先走信号线,然后进行电源的处理、电源的分割,然而电源的飞线是非常多的,非常影响信号线的布线,所以刚开始会将电源的飞线进行隐藏,具体操作的步骤如下所示:

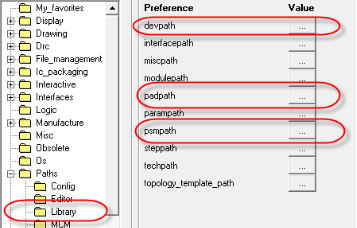

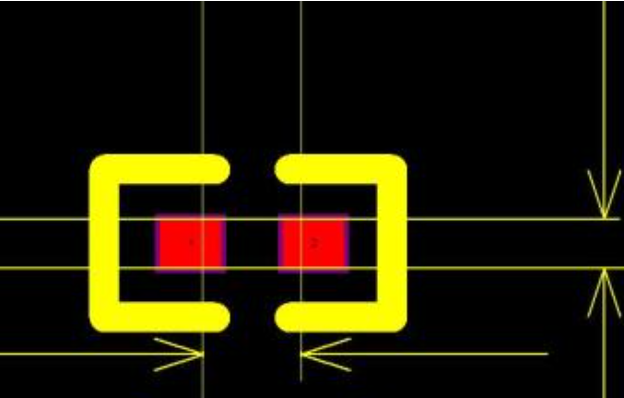

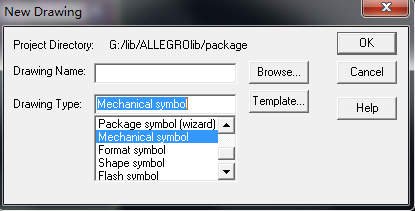

答:我们在PCB设计中,封装是一个非常重要的元素,我们在PCB设计之前,都需要先将所有的封装都处理好,才可以继续下一步的工作。所有这里我们讲解一下,在allegro软件中如何去指定PCB封装库的路径,需要指定哪几个路径改,如何在PCB中对指定封装库路径下的器件进行调用,具体操作如下:

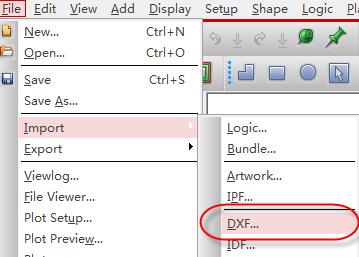

答:在上一问中我们讲解了PCB设计过程中,我们如何将结构工程师绘制的DXF文件导入到PCB中,那反过来,我们在PCB布局完成之后,需要核对结构是否有问题,是否满足要求,需要导出DXF文件,也是可以的,下面就详细介绍一下,如何通过allegro软件,导出DXF结构文件,具体的操作如下:

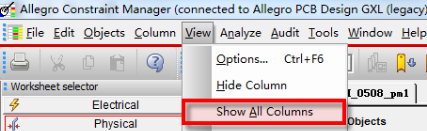

答:正常情况下CM规则管理器中属性较多,有很多列,如果有部分列我们不想显示,则可以隐藏,具体操作的步骤如下所示:第一步,点击Setup-Constraints-Constraint Manager选项,调出规则管理器。然后找到想隐藏的属性列(如Max Length),然后右击点击Hide Column选项,如图5-196所示,即可隐藏此列内容;

答:封装、焊盘设计统一采用公制系统,对于特殊器件,资料上没有采用公制标注的,为了避免英公制的转换误差,可以按照英制系统绘制。精度要求:采用mil为单位时,精确度为2;采用mm为单位时,精确度为4。

答:使用Orcad软件进行输出Allegro第一方网表时,弹出如图3-72所示的界面,这个是表示原理图有错误,不满足allegro软件的要求,不能输出网表, 图3-72 输出Allegro网表报错示意图在输出Allegro第一方网表弹出这个界面,我们需要找到如图3-72所示的netlist.log这个文件,原理图中存在的错误在这有详细的描述,这个文件一般存储于输出网表的那个文件夹下,用写字本文件打开此文件,如图3-73所示,将列表中所列的错误一一解决掉,即可输出网表文件了。

扫码关注

扫码关注