- 全部

- 默认排序

回答网友的问题:逻辑电路设计规则里gate width方向的尺寸一般要求远比feature size大,比如28nm的gate width最小也是100nm,间隔也最小80nm,这是出于什么考虑呢?有没有可能跟DRAM工艺那样,也压到fea

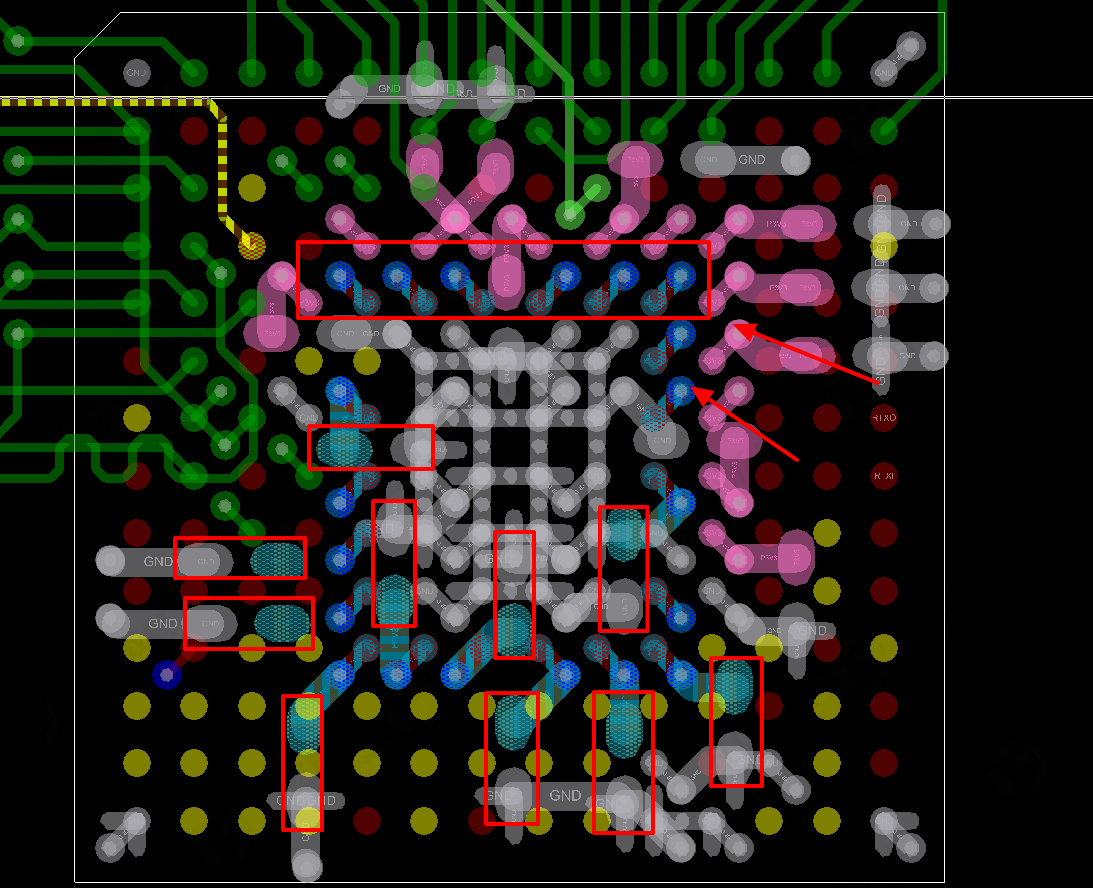

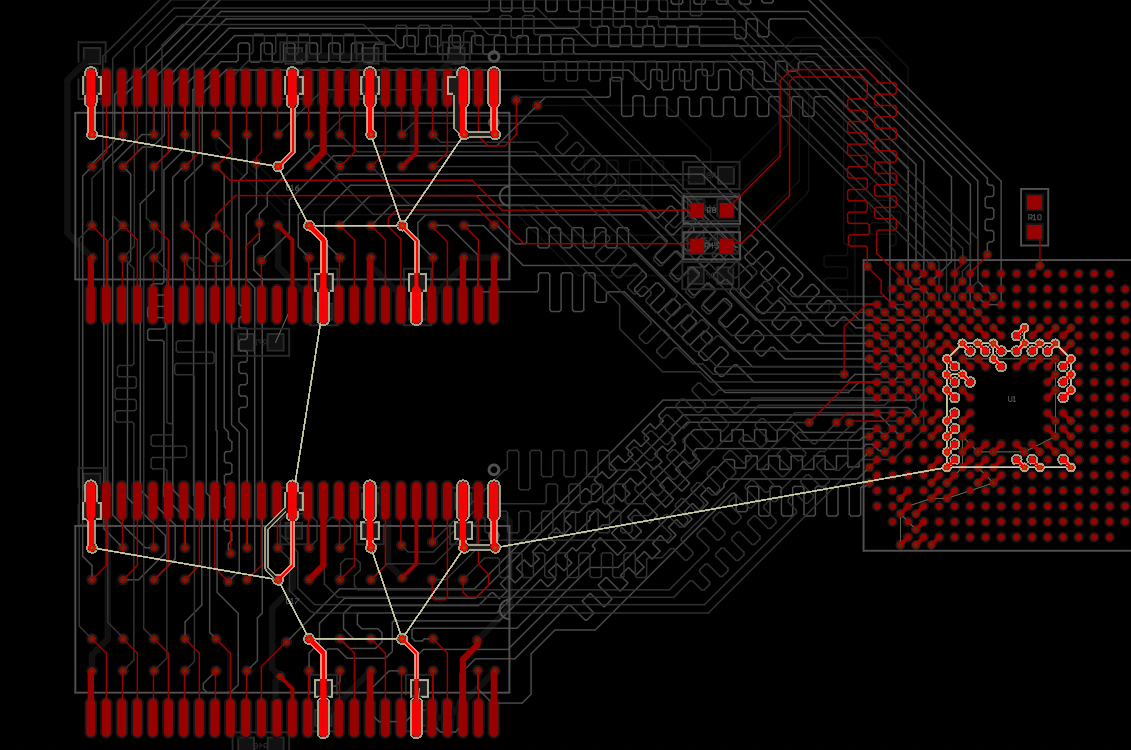

1.芯片下方电容要均匀分布。2.数据线等长组分组错误,两组线分别缺少LDOM、HDQM。3.数据线等长错误,应该控制误差50mil4.地址线等长分组错误,缺少部分网络5.电源输入线宽不一致,电容输入输出都需要加宽。6.多存在多处尖岬铜皮。7

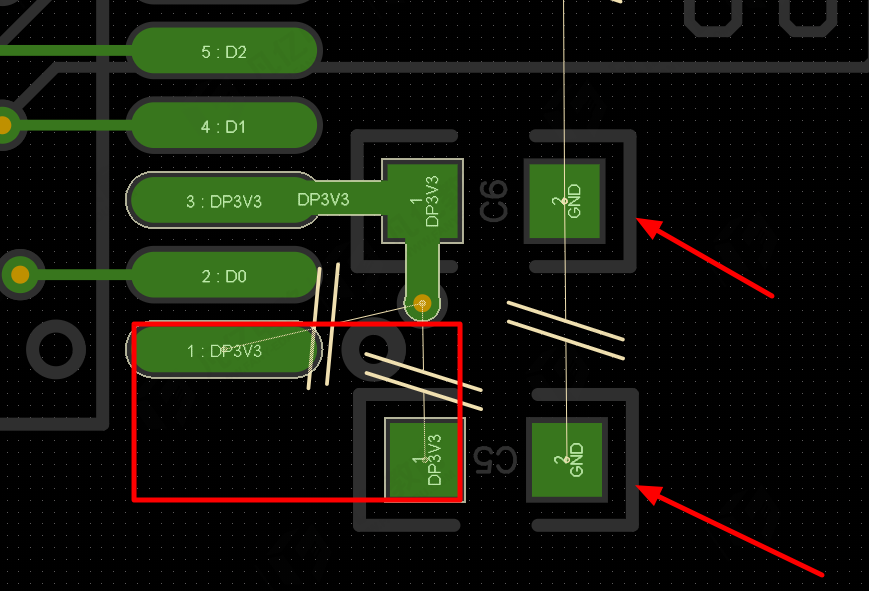

电源网络DP3V3全都是飞线显示,内层存在电源层赋予对应网络即可:电源平面层没有赋予网络,导致存在飞线网络没有连接:焊盘扇孔注意对齐,都没对齐,需要修改:类似这种过孔内存在线头的自己删除:注意走线优化:地址线内还存在误差报错:不需要拉线的地

SDRAM芯片引脚介绍

以 Micron公司容量为512Mb(512兆位),规格为8M×16×4的某款 SDRAM为例,介绍 SDRAM的引脚定义。(1) CLK:时钟信号,为输入信号。 SDRAM所有输入信号的逻辑状态都需通过CLK的上升沿采样确定。(2) (2)CKE:时钟使能信号,为输入信号,高电平有效。CKE信号的用途有两个,其是关闭时钟以进入省电模式,其二是进入自刷新( SELF REFRESH)状态。CKE无效时,SDRAM内部所有与输入相关的功能模块停止工作。在电路设计中需注意,应为C

时钟等长错误,按下方正确等长方法等长多处电源和地焊盘没有打孔导致开路地址线等长误差太大,地址线等长误差-+100mil电源没有连接,电源扇孔走线没有加粗以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问

近日,知名市场调查机构Yole Dédevelopement发布《内存行业年度状况报告》,报告中分析了2022年DRAM和NAND闪存芯片市场的发展趋势及预测,今天将为小伙伴们划出重点。报告中指出,2022年,DRAM市场将增长为25%,市

注意数据线之间等长需要满足3W2.次根信号等长不满足原理图要求3..地址线之间等长也需要满足3W4.存在开路以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item

答:PCB设计中常用的存储器有如下几种:Ø SDRAM,Synchronous Dynamic Random Access Memory(同步动态随机存储器)的简称,SDRAM采用3.3v工作电压,带宽64位,SDRAM将CPU与RAM通过一个相同的时钟锁在一起,使RAM和CPU能够共享一个时钟周期,以相同的速度同步工作,与 EDO内存相比速度能提高50%;

1.电源存在开路,地焊盘很多没有打孔造成开路报错。2.1v2电源过孔没有连通,造成天线报错。3.电源扇孔走线没有加粗4.时钟线电容应该考近芯片摆放5.时钟线等长错误,应与地址线放一组一起等长。6.地址线分组错误,缺少部分信号7.地址线等长错

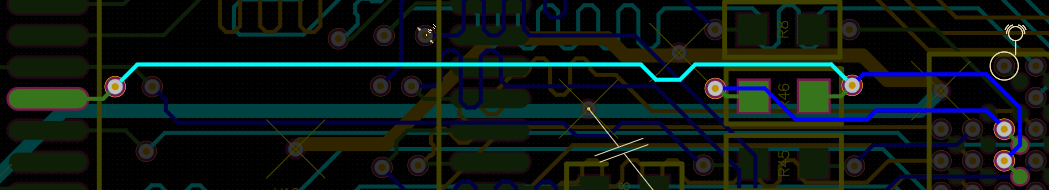

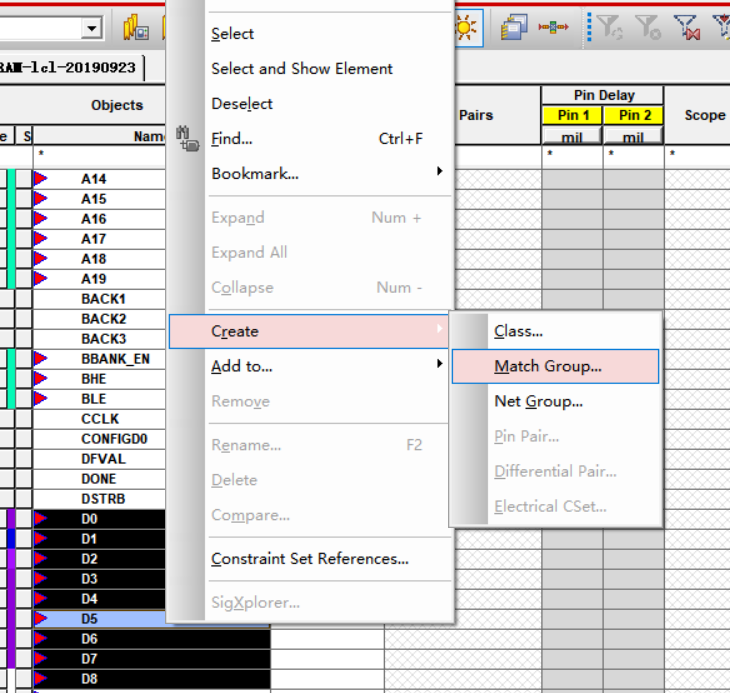

SDRAM信号线等长处理

在布线完成后,这里以SDRAM为例,要对SDRAM信号线进行等长处理,以满足时序要求。SDRAM的信号可分为数据线、地址线、控制线、时钟线,走线时要同组同层,间距满足3W原则,每组数据线的等长误差范围为+-50mil,地址线、控制线、时钟线的等长误差范围为+-100mil。

扫码关注

扫码关注