- 全部

- 默认排序

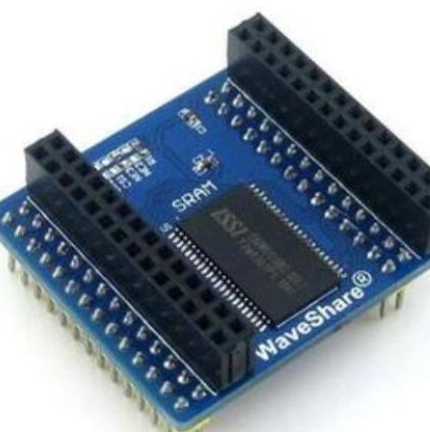

直播介绍:DDR SDRAM高速存储器是在高速PCB设计当中常见的模块,很多工程师对于如何处理单片、两片以及多片的布局、布线设计有很大的困惑,是一个设计难点。开设本次直播旨在全方位、多层次的去介绍DDR SDRAM高速存储器以及设计思路。直

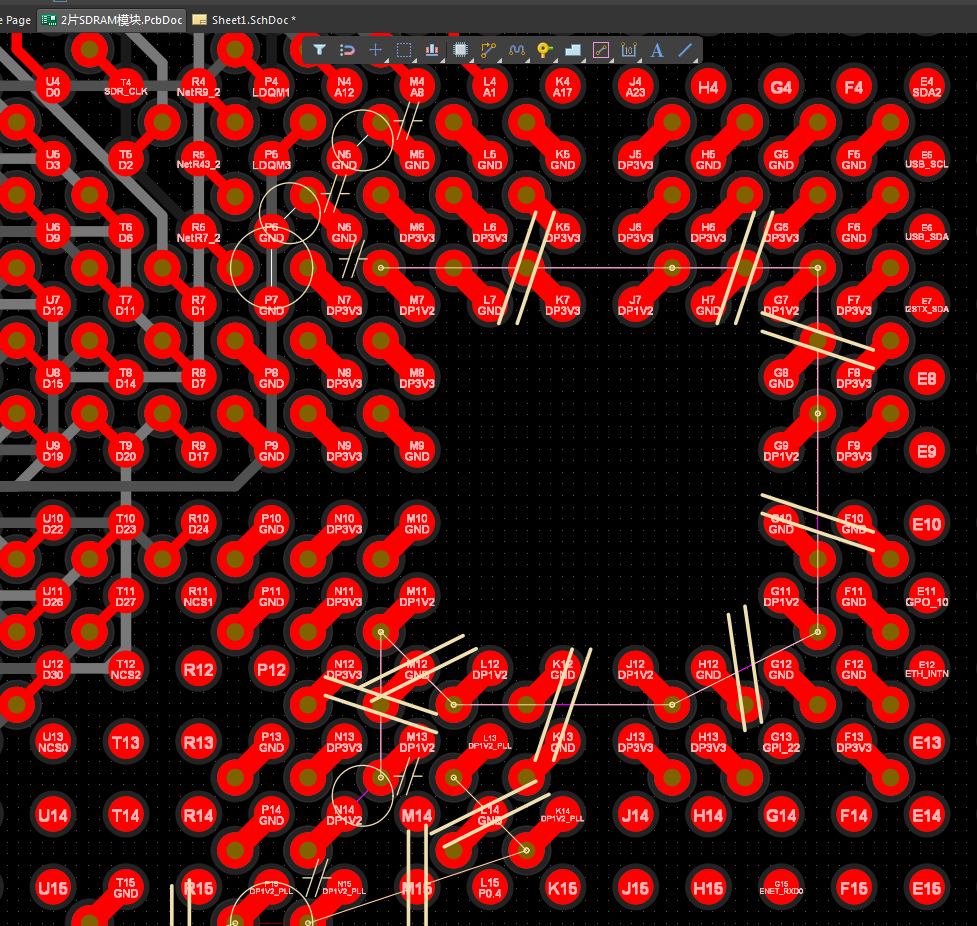

电源信号都没有处理:注意等长线的GAP尽量满足大于等于3W长度:可以减少串扰。注意看下xsignals分组 U16 -U17没有信号:数据跟地址用GND走线隔开:此处电源可以在电源层分割:以上评审报告来源于凡亿教育90天高速PCB特训班作业

SDRAM芯片引脚介绍

以 Micron公司容量为512Mb(512兆位),规格为8M×16×4的某款 SDRAM为例,介绍 SDRAM的引脚定义。(1) CLK:时钟信号,为输入信号。 SDRAM所有输入信号的逻辑状态都需通过CLK的上升沿采样确定。(2) (2)CKE:时钟使能信号,为输入信号,高电平有效。CKE信号的用途有两个,其是关闭时钟以进入省电模式,其二是进入自刷新( SELF REFRESH)状态。CKE无效时,SDRAM内部所有与输入相关的功能模块停止工作。在电路设计中需注意,应为C

SDRAM信号线等长处理

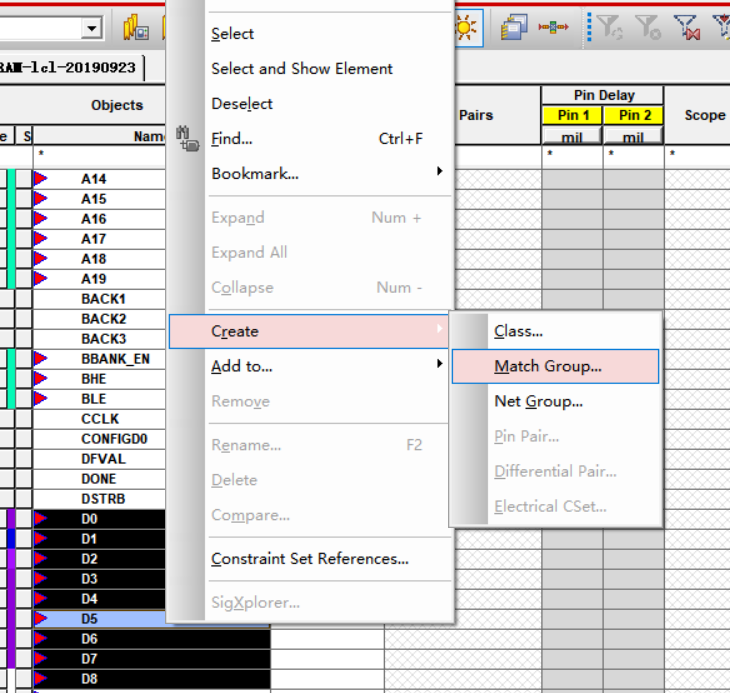

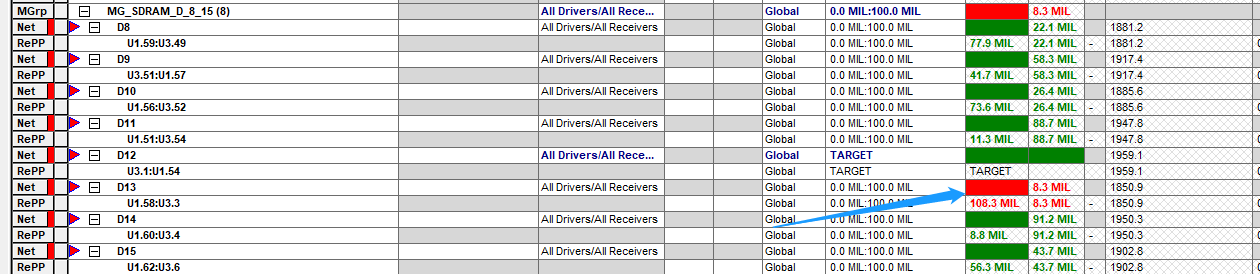

在布线完成后,这里以SDRAM为例,要对SDRAM信号线进行等长处理,以满足时序要求。SDRAM的信号可分为数据线、地址线、控制线、时钟线,走线时要同组同层,间距满足3W原则,每组数据线的等长误差范围为+-50mil,地址线、控制线、时钟线的等长误差范围为+-100mil。

器件摆放干涉2.走线尽量不要从小器件中间穿3.数据线等长误差+-25mil,也就是50mil,后期自己重新设置一下4.地址线误差是+-50mil5.数据线等长存在误差报错地址线也存在同样的问题,后期自己绕一下蛇形等长6.数据线和地址线之间最

1SDRAM注意数据线等长存在报错2DDR注意差分出线呀尽量耦合2.差分线对内等长处理不当,锯齿状等长不能超过线距的两倍3.差分要设置对内等长误差5mil4.滤波电容尽量保证一个管脚一个,靠近管脚摆放5.注意电源管脚扇孔走线需要加粗以上评审

线宽不一致,导致阻抗不连续走线需要保持3w间距规则地址线分组错误,缺少信号时钟线等长错误电源走线多处没有加粗数据线等长误差控制100mil范围内以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫

晶振需要走内差分处理2.SDRAM数据线低八位和高八位需要分开创建class,分别进行等长3.注意数据线之间等长需要满足3W规则4.地址线也需要满足3W规则5.滤波电容靠近管脚放置,尽量保证一个管脚一个6.数据线等长误差建议+-25,mil

答:PCB设计中常用的存储器有如下几种:Ø SDRAM,Synchronous Dynamic Random Access Memory(同步动态随机存储器)的简称,SDRAM采用3.3v工作电压,带宽64位,SDRAM将CPU与RAM通过一个相同的时钟锁在一起,使RAM和CPU能够共享一个时钟周期,以相同的速度同步工作,与 EDO内存相比速度能提高50%;

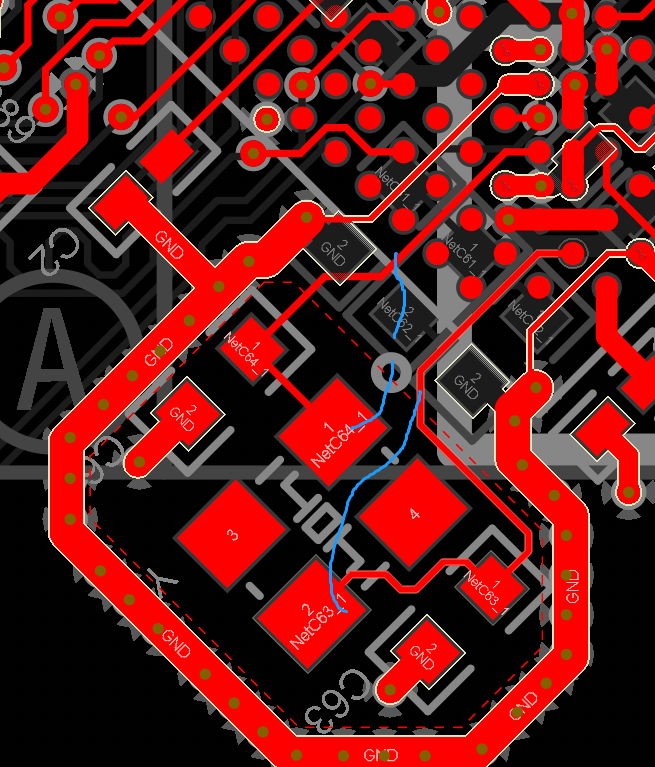

1.配置电容要均匀的分配到电源管脚靠近放置。2.多处单端网络扇孔没有删除导致天线报错,无网络焊盘打孔导致短路报错3.bga扇孔存在短路4.电源走线没加粗。5.地网络没打孔导致开路报错,地网络应就近打孔。6.信号线布线造成闭合回路。7.等长注

全站最新内容推荐

- 1常规变压器耦合型自激调频式开关电源电路分析讲解

- 2低压MOS在多电平逆变器上的应用-REASUNOS瑞森半导体

- 3走进电子元件,了解双稳态触发器

- 4模拟电路太难读?有没有可能是你不会看!

- 5要使用电烙铁,应该注意什么?

- 6硬件设计:4.10 通过这个实验,你会深刻认识到电感滤波与电容滤波电路的区别(为什么电容型滤波电路不能用在大电流环境)

- 7硬件设计:4.8-4.9 电感教程_滤波电路_低通滤波电路为什么分为电容型和电感型

- 8硬件设计:4.7电感教程_为什么有些开关电源在上电时会过压_怎么解决

- 9硬件设计:4.6 电感教程_5V电压升至1万V电压的工作原理

- 10硬件设计:4.5 电感教程之开关电源教程(boost型)_重新认识电感的重要性

扫码关注

扫码关注