- 全部

- 默认排序

Allegro经常导出STP文件后。用Catia无法打开是怎么回事?要不就是丢失部分铜皮。

当对Allegro软件PCB层叠结构进行设置的时候,某一层可以设置为plane或者conduct,平面层和走线层。但是我发现无论是设置成plane还是conduct,这一层都可以走线,手动铺铜皮,edit-split creat这样去灌铜进行铜皮分割。既然这样,那么设置层的时候,plane和cond

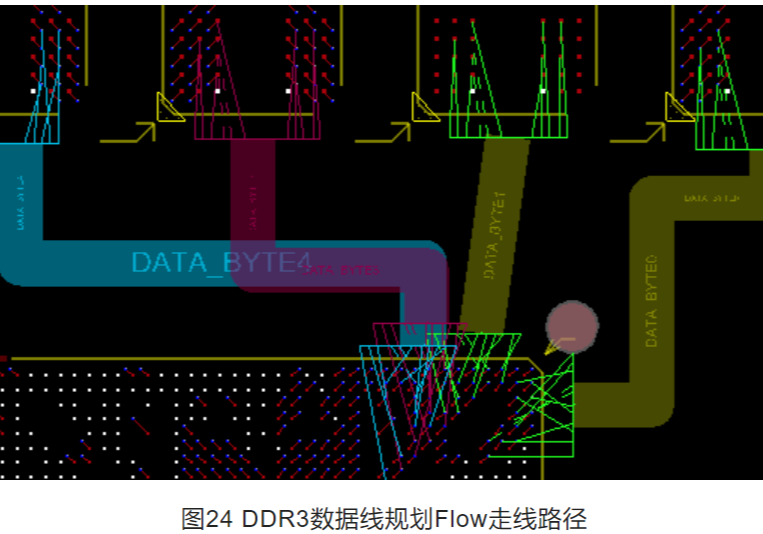

GRE是Global Route Environment的缩写,中文意思为全局布线环境,运用具备阶层化意识的全面绕线引擎与图形式互连流程规划程序。通GRE技术在短时间就可以开发出包含众多互连总线与芯片引脚数的复杂且高速的设计组件。此外,运用

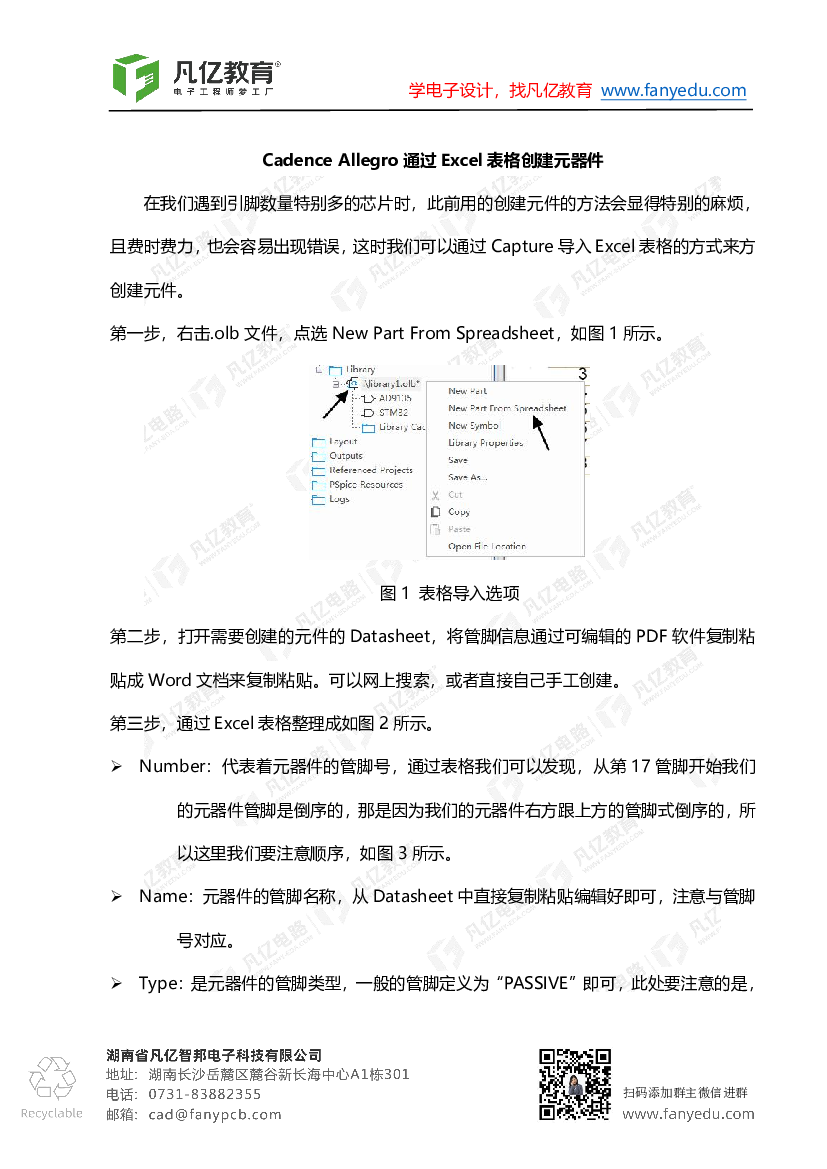

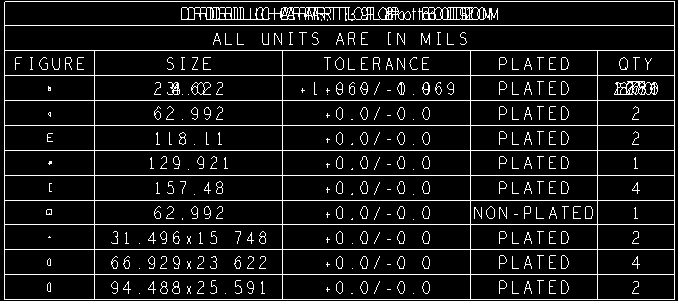

答:添加钻孔表格时,有时候系统自动生成的表格数据是重叠的,如图6-291示。

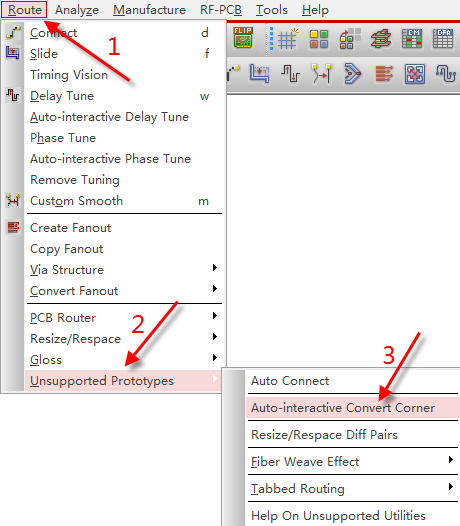

答:一般我们在处理PCB走线的时候,都是45度走线,当遇到比较高速的信号时,为了满足阻抗的一致性,可以设置成为圆弧走线,在16.6版本以后,可以对45度的走线自动转换为圆弧的功能,具体操作如下:

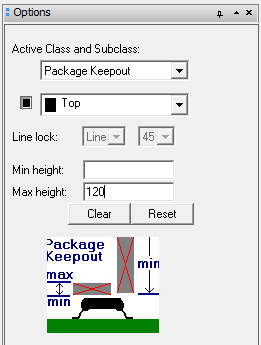

答:我们在进行一些复杂的PCB设计时,都会有很多结构限制,比如这里限高3MM等需求,为了辅助工程师们更好的进行设计,我们需要在PCB区域内绘制限高区域,并设置限高的参数,具体操作如下所示:第一步,在PCB板上绘制需要限高的区域,执行菜单命令Setup-Areas,在下拉菜单中选择Package Keepout,如图5-66所示,显示器件禁布区。

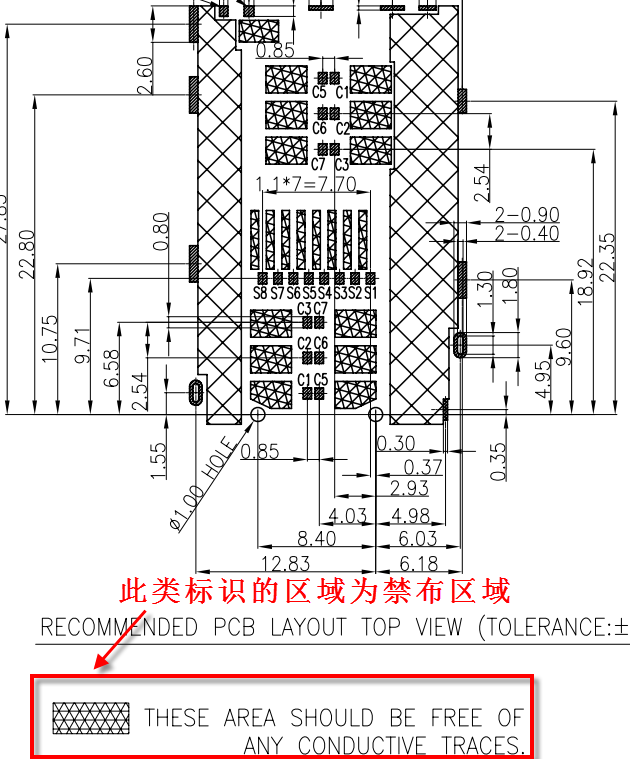

答:在PCB封装中,出现以下情况需要画Keepout层,一般绘制在Route Keepout、Via Keepout层。第一,如果Datasheet中指明了需要画Keepout层,则需要绘制Keepout层,绘制的大小按照Datasheet中指定的大小,如图4-122所示,

全站最新内容推荐

- 1Intel:2030年全球50%半导体由美欧制造

- 2全球首款有256核心的处理器正式发布!

- 3施密特触发电路、单稳态电路、多谐振荡电路

- 4BGA焊点容易氧化,是什么原因?

- 5VKL128点阵式液晶显示IC高抗干扰液晶段码屏驱动

- 6通过 SmartConnect 技术简化 IP 集成,XCKU15P-1FFVA1760E、XCKU15P-2FFVA1760E现场可编程门阵列规格参考

- 7永嘉微超强抗干扰触控VK36N5D五键触摸触控芯片,适用于家电触摸感应IC等等

- 8电路设计:如何提高信号链前端增益?

- 9FPGA应用,XCKU5P-2FFVA676E XCKU5P-L2FFVB676E XCKU5P-3FFVB676E能够驱动 16G / 28G 背板的收发器

- 10走进电子材料,了解N型半导体

扫码关注

扫码关注