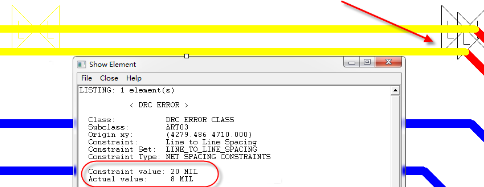

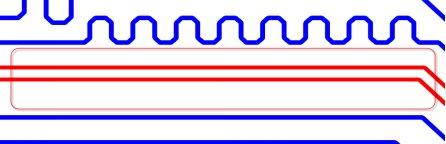

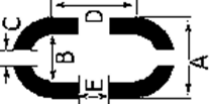

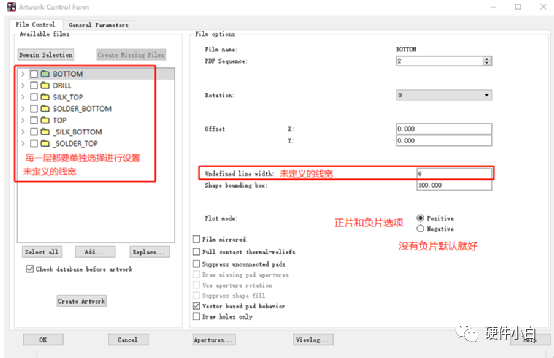

答:我们在PCB设计过程中,差分信号是比较重要的信号,一般设置差分信号到其它信号的间距是20mil,但是设置完差分信号到其它信号的间距之后,差分对内PN之间不满足20mil的间距,会报错,如图6-205所示:

图6-205 差分信号对内报错示意图

如图6-205所示,差分信号到其它信号的间距是20mil,但是差分按照阻抗线宽走线,间距是8mil,所以出现DRC的错误。

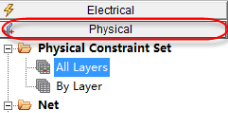

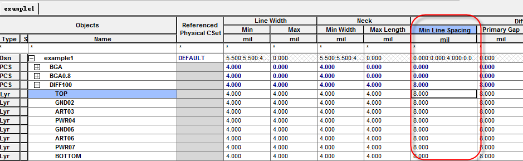

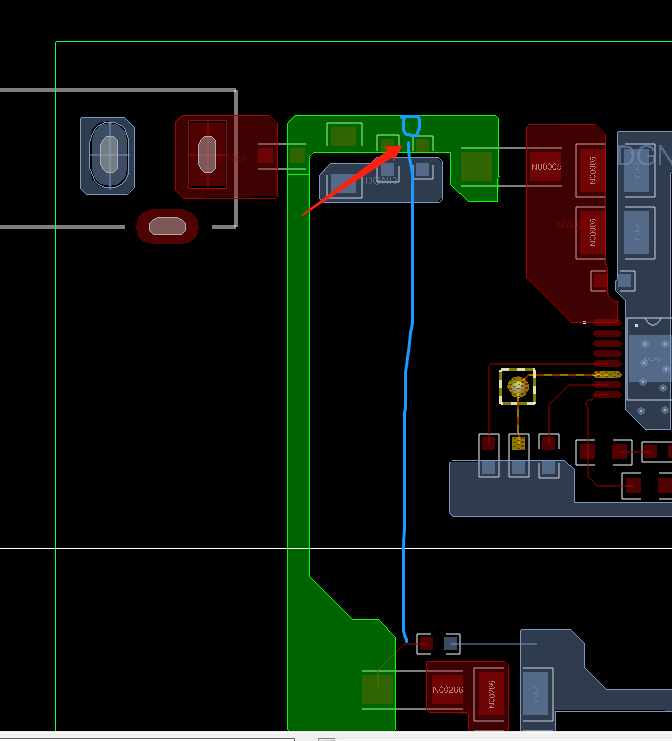

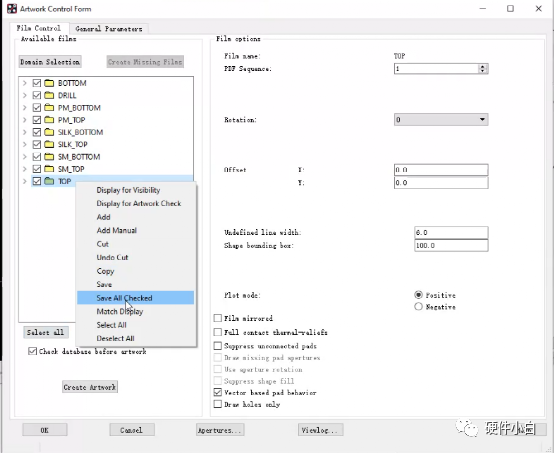

第一步,打开规则管理器,执行菜单命令Setup-Constrains,在下拉菜单中选择Constraint Manager,进行规则设置,左侧选择Physical Constraint Set,如图6-206所示,点击all layers;

图6-206 进入物理规则设置示意图

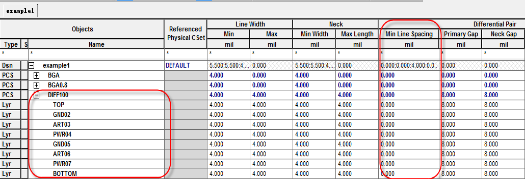

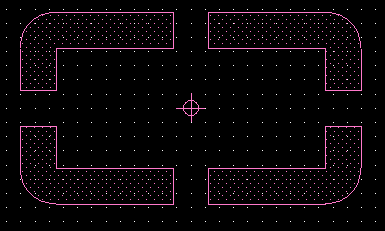

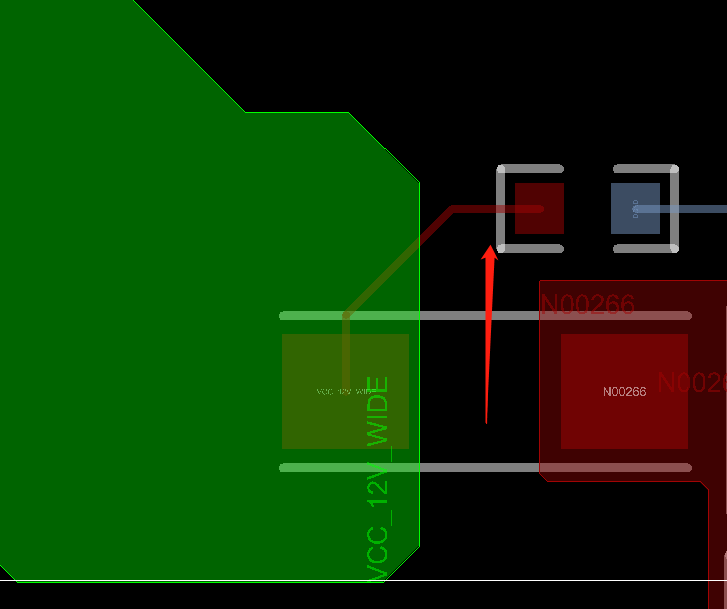

第二步,差分走线设置的规则,是DIFF100的规则,在差分属性的Min Line Spacing最小间距,目前是0,如图6-207所示,我们将其设置为差分默认的间距8mil,如图6-208所示;

图6-207 默认差分间距设置示意图

图6-208 差分最小间距设置示意图

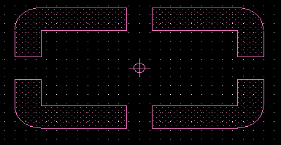

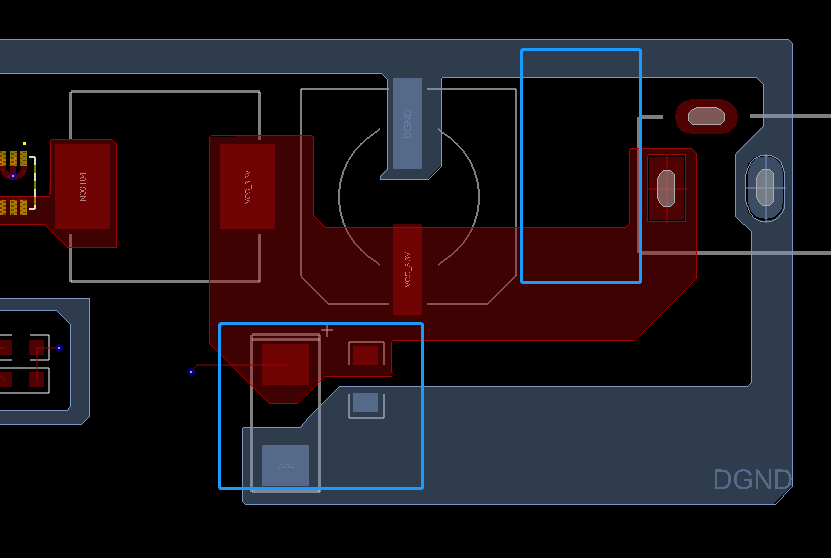

第三步,设置完成以后,回到PCB界面,如图6-209所示,差分线已经不会报错了,对内满足阻抗要求,对外到其它信号满足20mil间距。

图6-209 差分信号不报错示意图

扫码关注

扫码关注

![Z变换的性质及定理 [学以致用系列课程之数字信号处理]](https://api.fanyedu.com/uploads/image/0c/d17b51410a6f06e152c6538df4cb9b.png)