虽然市场上仅有苹果的A17 Pro芯片用上了台积电的3nm工艺,但台积电的雄心远不止于此,不仅在明年全面铺开N3E工艺,还要筹备更高的制程工艺,如2nm,甚至1nm。

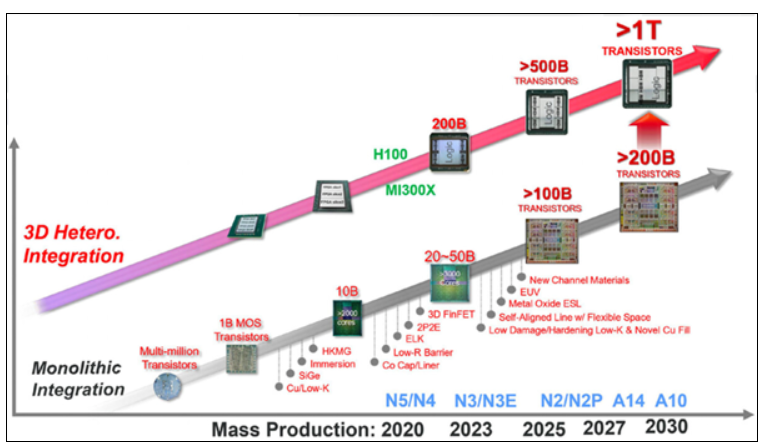

据外媒tomshardware报道,台积电近日在IEDM大会上发布了最新的路线图,并公布计划在2030年推出1nm级的A10制程,实现单个芯片上集成2000亿个晶体管,并依托于先进封装技术,实现单个封装上集成1万亿个晶体管的目标。

由图可知:台积电首先将在2025年量产2nm的N2制程,然后在2026年左右量产N2P制程,届时将采用新的通道材料、EUV、金属氧化物ESL、自对齐线w/Flexible Space、低损伤/硬化Low-K&新型铜填充等技术。最后实现单颗芯片集成超过1000亿个晶体管,同时借助先进的3D封装技术,实现单个封装集成超过5000个晶体管。

在2027年后,台积电将量产1.4nm级的A14制程,最终在2030年量产1nm的A10制程,实现单芯片集成度超过2000亿个晶体管,借助D封装技术,实现单个封装内集成超过1万亿个晶体管。

扫码关注

扫码关注