- 全部

- 默认排序

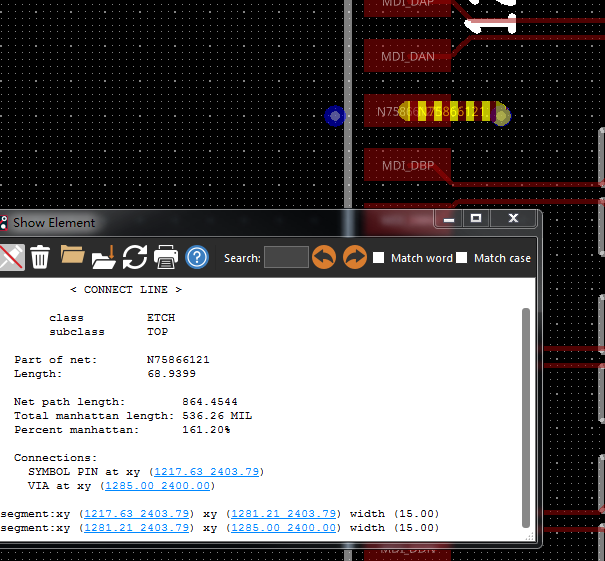

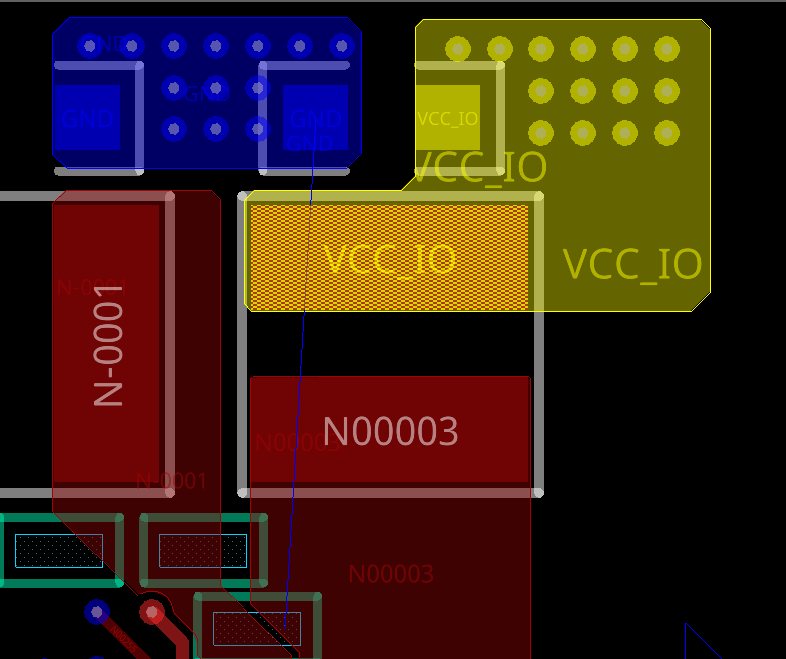

变压器除差分信号 其他信号20MIL:晶振注意做个包地:注意机壳地跟电路地在空间充足的情况下隔离2MM宽度:扇孔不整齐:差分以及RX TX等长没什么问题。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访

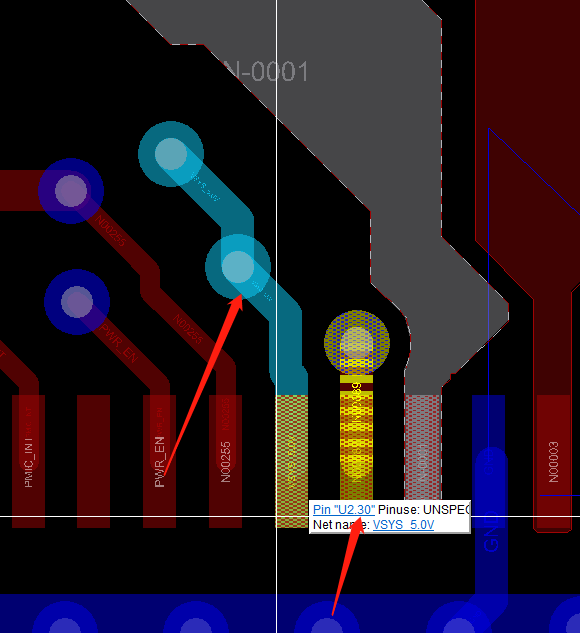

还有地网络并未处理,还有飞线:对应器件就近管脚放置:过孔数量根据载流大小计算下个数,再加2-4个过孔的裕量就可以了:底层器件尽量整体中心对齐放置:以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或

在现代电子设计中,高速信号的传输变得越来越常见,然而高速信号传输过程中总会遇见信号耦合和串扰等问题,这些现象将导致信号完整性的损坏,从而影响系统的性能和可靠性,那么下面将聊聊如何解决信号耦合和串扰等问题。1、信号耦合和串扰的产生高速信号传输

在现代高速电子设备中,PCB板的阻抗测量和控制是至关重要的技术,准确的阻抗设计和测量可确保产品的信号完整性、抑制信号串扰及提高系统性能,因此是很多电子工程师的重点学习内容,下面聊聊PCB阻抗测量及控制方法。一、PCB板上如何测量阻抗?1、T

随着微电子技术和信息技术的高速发展,越来越多的企业开始入局半导体领域,和半导体息息相关的电子工程师岗位也开始成为当下最火的高薪工作首选,这也吸引很多人去选择电子工程师,今天我们将分享四个电子工程师面试会问到的问题,希望对小伙伴们有所帮助。1

数字芯片作为计算机系统必不可少的核心芯片,随着5G大规模应用,开始高速发展,和模拟芯片逐渐成为电子工程师的日常研究芯片之二,今天我们来聊聊数字芯片后端设计流程,希望对小伙伴们有所帮助。1、数据准备对于Cadance的SE而言后端设计所需的数

高速设计已成为愈来愈多 PCB 设计人员关切的重点。在进行高速 PCB 设计时,每位工程师都应重视其信号完整性,并且需时常考虑其信号电路的回流路径,因为不良的回流路径容易导致噪声耦合等信号完整性问题。如果电流必须经过很长的路径才能返回,信号路径的电感回路会增加。当系统中的电感回路越大,这些信号愈有可

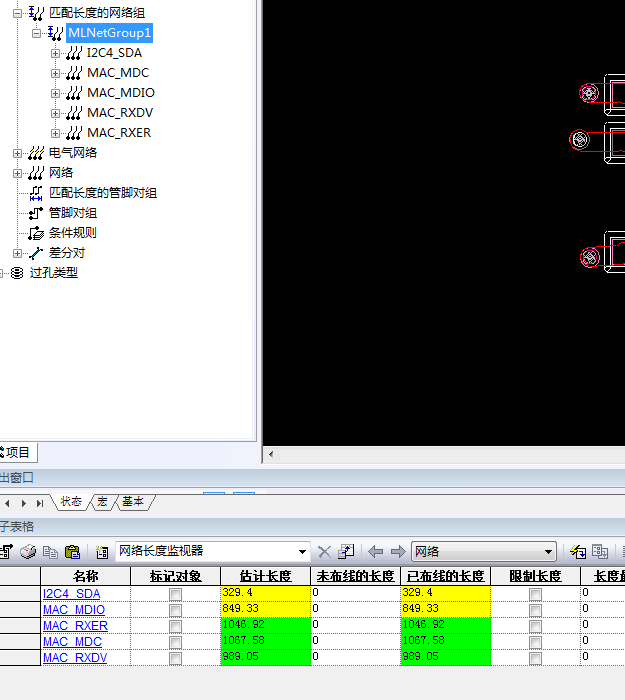

是需要将RX TX分组等长,看下自己的分组:还需要创建TX匹配长度网络组设置好误差进行等长。注意电源信号铺铜连接尽量均匀:差分等长没啥问题。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联

此处电源输入打两个过孔不满足载流2.线宽尽量保持一致3.主电源应该铺铜满足载流4.器件摆放干涉5.器件摆放尽量中心对齐以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https:/

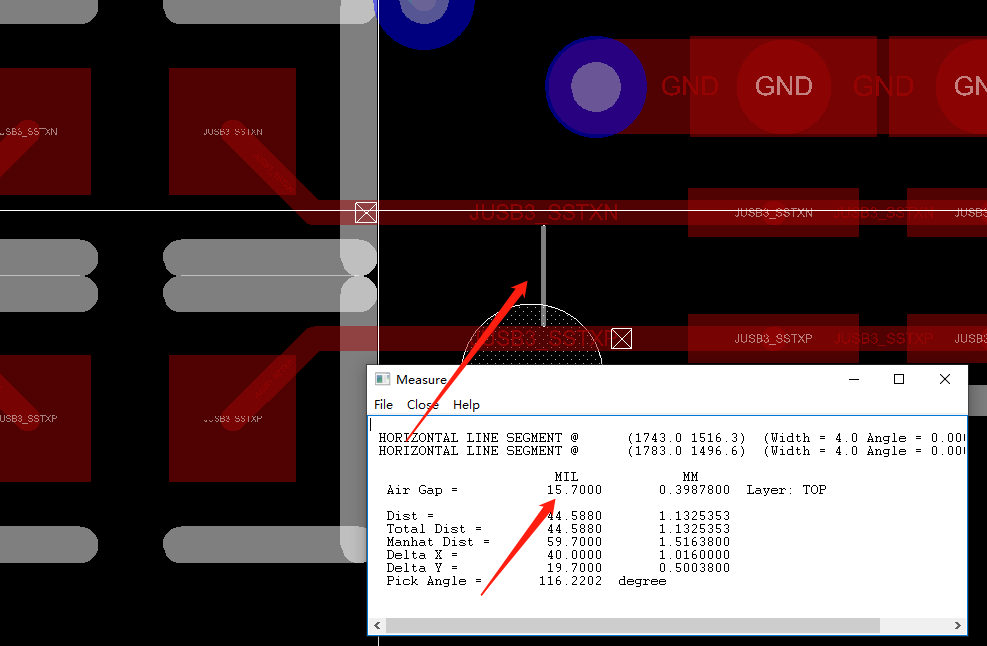

差分走线不满足差分间距规则2.锯齿状等长不能超过线距的两倍3.差分对内等长误差5mil4.ESD器件尽量靠近接口管脚放置5.包地 地线上尽量多打地过孔以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访

扫码关注

扫码关注