- 全部

- 默认排序

差分走线需要保持耦合从过孔内拉出:此处差分亚需要重新拉出耦合走线,并且差分对内等长需要注意规范:注意高度要小于2S。板上多余线头删除掉:其他的没什么问题了。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以

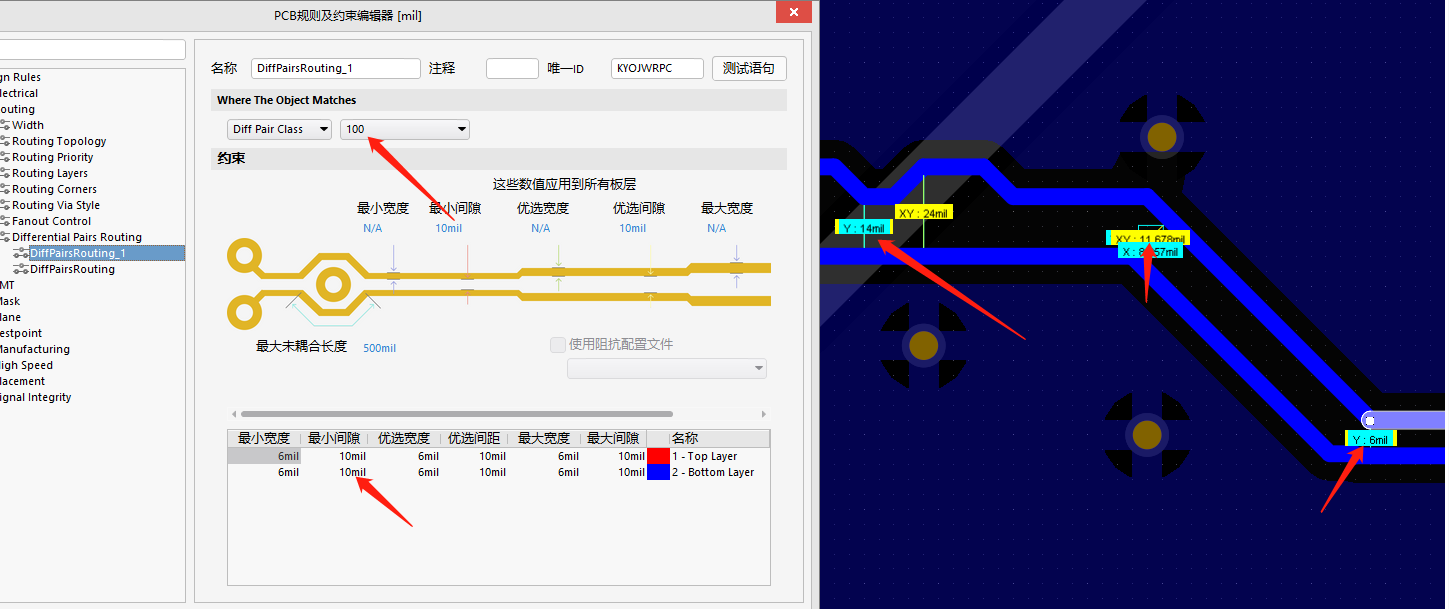

差分走线不符合规范,要按照差分阻抗线宽线距进行走线2.对内等长凸起高度不能超过线距的两倍3.差分走线需要在优化一下4.此处存在短路5.存在多处开路6.一层连通不用打孔,差分要按照阻抗线距走线7.时钟信号尽量单根包地处理8.差分对内等长误差5

电子人都知道,FPGA是高度集成的芯片,具有大量可配置逻辑块和I/O(输入/输出)接口,因此需要精确的电源管理来满足其运行需求,然而这并非容易得事情,在选择电源方案时需要考虑多种因素,以确保稳定、可靠的性能。1、为什么选择电源解决方案很重要

近年来,随着科技不断发展,越来越多新兴事物出现在工业上,焊接机器人就是其中之一。焊接机器人是一种高度自动化的焊接设备,它的应用,可以提高焊接质量、减少人力成本,改善运作环境,以诸多优势被国内国外厂商接受并应用。小白实战速成PCB设计,零基础

IPQ8074是一款高度集成的SoC,旨在面向下一代企业接入点、运营商网关和消费级路由器,提供最大化的容量、最广泛的覆盖及最优的性能。该产品集成了四个 Cortex-A53核心以及双核的网络加速器,支持2.4GHz上4X MU-MO和Hz上

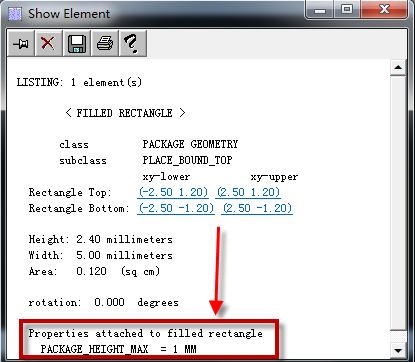

答:在做PCB设计时,有时结构上会对局部的器件布局有高度要求,不能将超过高度限制的器件放到限高区,否则会导致PCB装配问题。这个高度信息我们可以在做PCB封装时进行设置,设置好了就可以在设计时查看高度信息,辅助我们进行PCB设计。第一步,打开一个PCB封装,将Package Geometry-Place_Bound_top层显示出来,如图4-70所示, 图4-70 显示元器件占地面积示意图第二步,点击Setup-Areas-Package Height选项,如图4-71所示

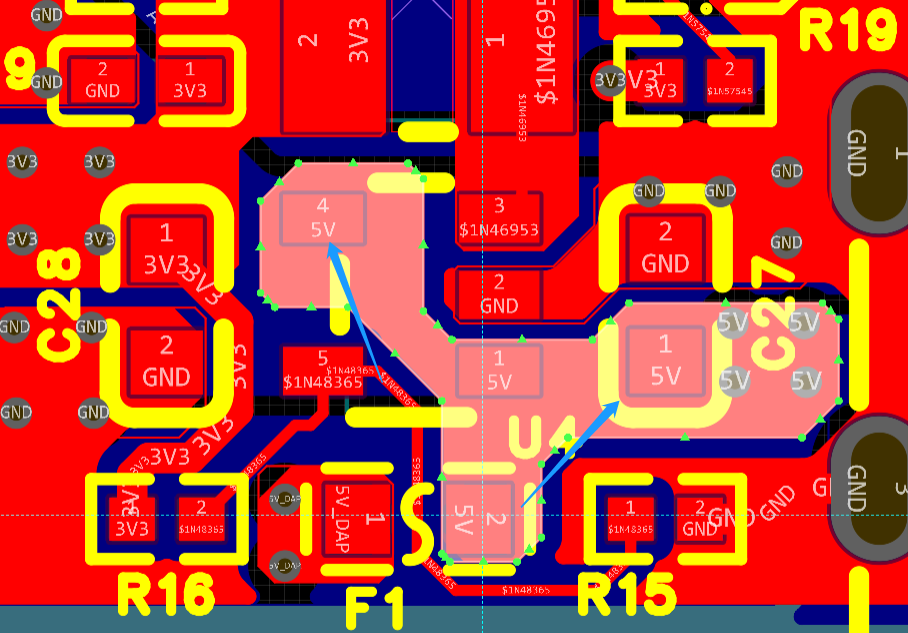

1.电源输入的滤波电容应该靠近输入管脚(4脚)放置2.走线尽量不要从器件中间穿,自己调整一下走线路劲3.此处出线载流瓶颈,载流计算都是以铜皮在窄处进行计算4.差分线处理不当,锯齿状等长,凸起高度不得超过线距的两倍5.器件摆放尽量对齐处理6.

答:翘曲度(warpage or warp),用于表述平面在空间中的弯曲程度,在数值上被定义为翘曲平面在高度方向上距离最远的两点间的距离。绝对平面的翘曲度为0。

瑞萨电子推出具备超低静态电流的升降压DC/DC转换器-支持旁路模式的ISL9122A具有高度灵活性,可显著延长无线与智能物联网设备的电池寿命

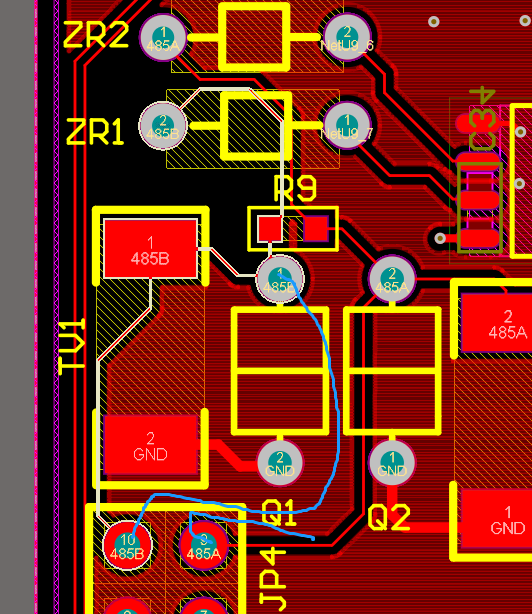

注意485需要走类差分形式2.跨接器件旁边要尽量多打地过孔,间距要最少要1.5mm3.差分对内等长凸起高度不能超过线距的两倍4.差分出线要尽量耦合5.模拟信号需要加粗处理6.反馈信号需要加粗到10mil7.注意数据线之间等长需要满足3W规则

扫码关注

扫码关注