- 全部

- 默认排序

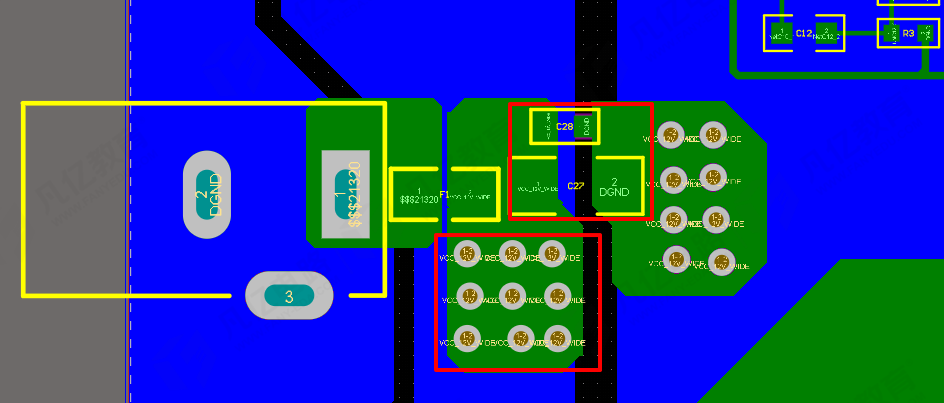

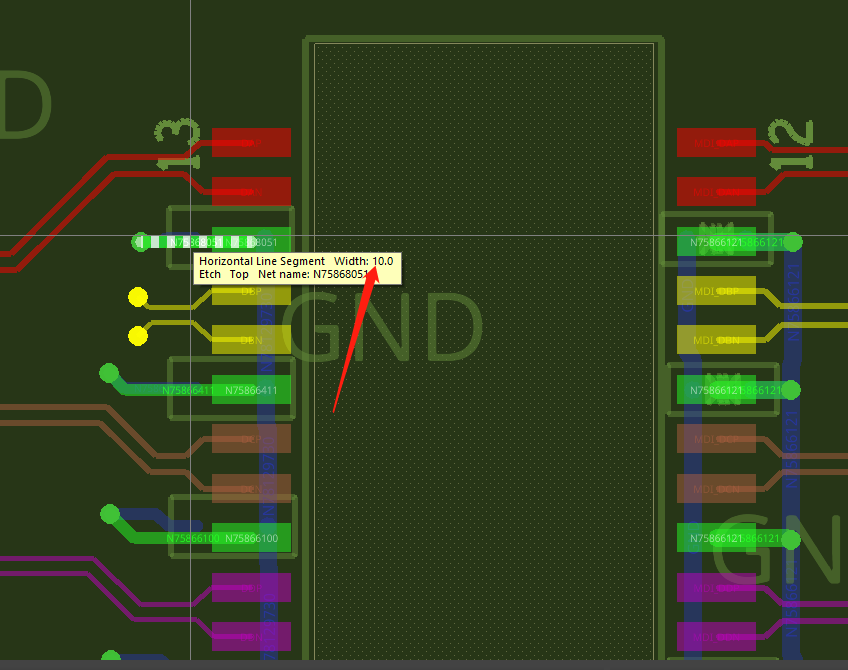

电容按照先大后小原则放置,过孔打在最后一个电容后方输入电源过孔打在第一个器件前方反馈信号过孔走线没有信号电源主输出路径没有连接,应从Q2器件铺铜连接到大电感过孔尺寸过大,常用过孔尺寸一般是8-16、10-20等除散热孔外其他过孔盖油处理以上

注意电源不要任意角度走线,注意走线规范:此处电池管脚加粗走线:铺铜注意这种尖岬铜皮,自己优化下:注意走线能拉直的拉直处理,尽量最短路径:此处器件包地处理:还存在一处开路报错:以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解P

除了元器件的选择和电路设计之外,良好的印制电路板(PCB)设计在电磁兼容性中也是一个非常重要的因素。PCB EMC设计的关键,是尽可能减小回流面积,让回流路径按照设计的方向流动。最常见返回电流问题来自于参考平面的裂缝、变换参考平面层、以及流经连接器的信号。跨接电容器或是去耦合电容器可能可以解决一些问

一个良好的布局设计可优化效率,减缓热应力,并尽量减小走线与元件之间的噪声与作用。这一切都源于设计人员对电源中电流传导路径以及信号流的理解。 当一块原型电源板首次加电时,最好的情况是它不仅能工作,而且还安静、发热低。然而,这种情况并不多见。

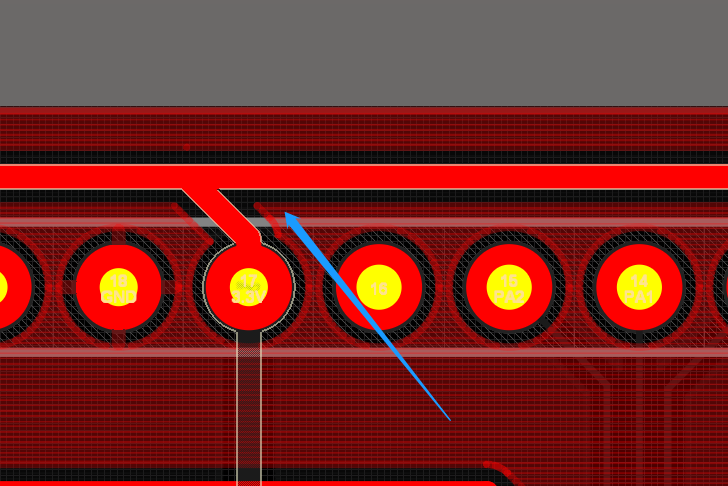

ReturnPath回流路径高速设计已成为愈来愈多PCB设计人员关切的重点。在进行高速PCB设计时,每位工程师都应重视其信号完整性,并且需时常考虑其信号电路的回流路径,因为不良的回流路径容易导致噪声耦合等信号完整性问题。如果电流必须经过很长的路径才能返回,信号路径的电感回路会增加。当系统中的电感回路

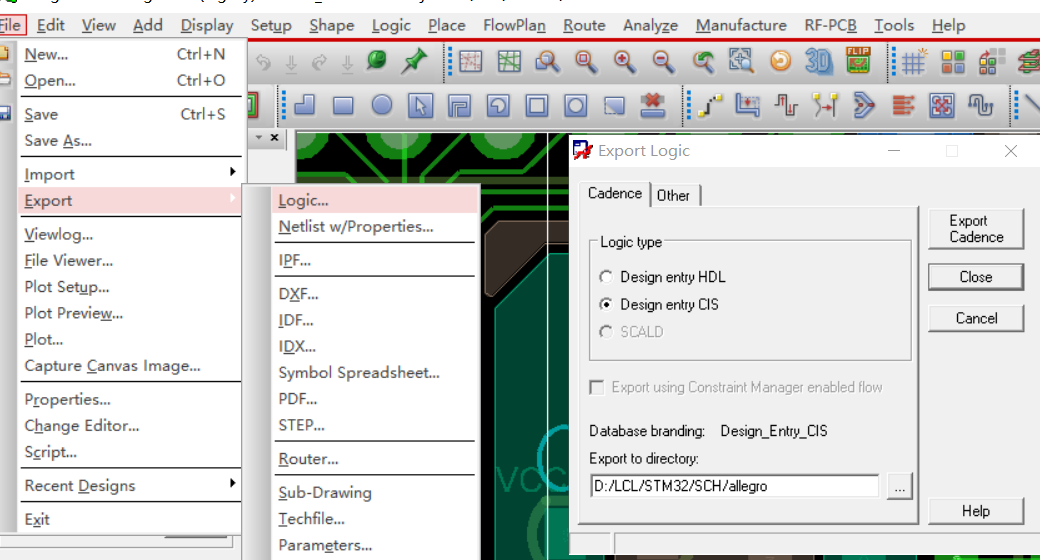

弹出export logic对话框,选择design entry CIS选项,export directory选择输出网表的路径,然后单击export directory按钮。导出完毕后,单击close按钮,关闭对话框。用orcad打开与PCB相对应的原理图,执行菜单命令tools→back annotate.....,在弹出的back annotate对话框中打开PCB editor选项卡,如图:

注意单点接地,此处不用打孔,只需要在芯片中心打孔进行回流即可2.电感所在层的内部需要挖空处理3.器件摆放注意对齐4.走线可以离测试点远点,后期自己调整一下走线路径5.反馈线走10mil即可6.注意电源输入需要打孔在底层进行连接输出打孔打在滤

AD系统自带的原理图库的路径是(AD20版本)C:\Users\Public\Documents\Altium\AD20\Library(默认安装在C盘,前面路径为软件的安装路径)后缀为IntLib 的文件就是。此文件为集成库文件,是把PC

注意变压器除差分信号外,其他信号走线需要加粗处理2.电容尽量靠近管脚均匀摆放3.地网络需要就近打孔,连接到地平面4.注意晶振需要包地处理5.走线间距太近,后期容易造成短路,自己后期优化一下走线路径6.走线等长线之间需要满足3W规则7.时钟信

RK3588 VDD_CPU_LIT电源PCB设计1、VDD_CPU_LIT覆铜宽度需满足芯片电流需求,连接到芯片电源管脚的覆铜足够宽,路径不能被过孔分割太严重,必须计算有效线宽,确认连接到CPU每个电源PIN脚的路径都足够。2、VDD_C

扫码关注

扫码关注