- 全部

- 默认排序

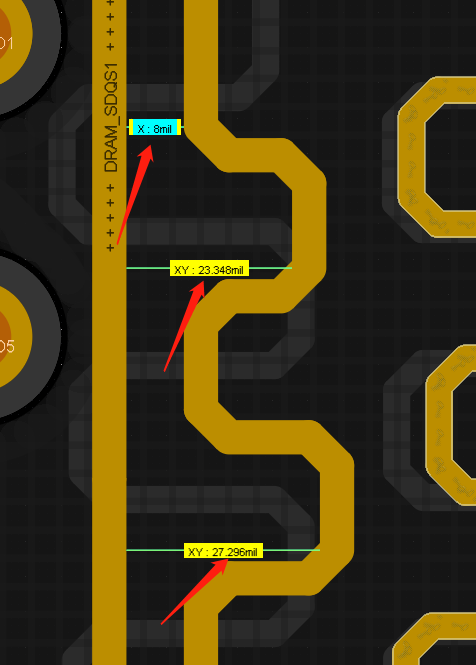

差分信号打孔换层 注意两侧打上地过孔,缩短回流路径:注意器件尽量整体中心对齐:过孔注意间距,不要造成平面割裂:变压器上除了差分信号 其他的加粗20MIL:差分对内等长误差控制在5MIL:RX TX需要对内做等长以上评审报告来源于凡亿教育90

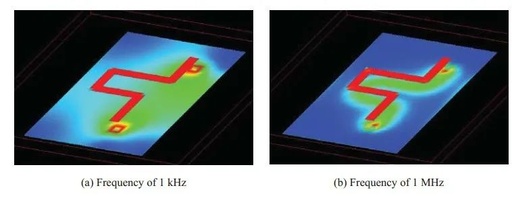

ReturnPath回流路径高速设计已成为愈来愈多PCB设计人员关切的重点。在进行高速PCB设计时,每位工程师都应重视其信号完整性,并且需时常考虑其信号电路的回流路径,因为不良的回流路径容易导致噪声耦合等信号完整性问题。如果电流必须经过很长的路径才能返回,信号路径的电感回路会增加。当系统中的电感回路

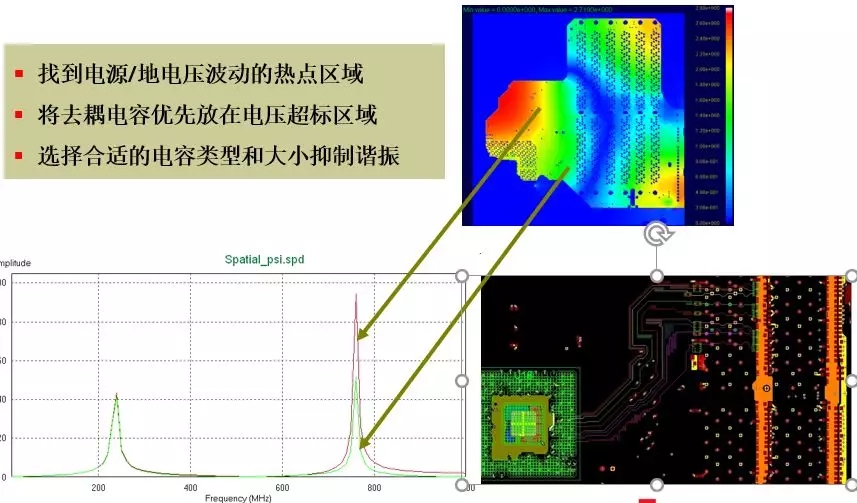

Sigrity PowerSI是IC封装和PCB设计快速准确的全波电磁场分析,作为专业的频域分析工具,为当前高速电路设计中面临的各种信号完整性(SI)、电源完整性(PI)和电磁兼容(EMI/EMC)分析提供快速准确的全波电磁场分析,并提供宽带 S参数提取以及频域仿真。PowerSI可以为IC封装和PCB设计提供快速准确的全波电磁场分析,从而解决高速电路设计中日益突出的各种PI和SI问题:如同步切换噪声(SSN)问题,电磁耦合问题,信号回流路径不连续问题,电源谐振问题,去耦电容放置不当问题以及电压

答:我们PCB中的信号都是阻抗线,是有参考的平面层。但是由于PCB设计过程中,电源平面的分割或者是地平面的分割,会导致平面的不完整,这样,信号走线的时候,它的参考平面就会出现从一个电源面跨接到另一个电源面,这种现象我们就叫做信号跨分割。跨分割的现象如图1-52所示。跨分割,对于低速信号,可能没有什么关系,但是在高速数字信号系统中,高速信号是以参考平面作为返回路径,就是回流路径。当参考平面不完整的时候,会出现如下影响:Ø 会导致走线的的阻抗不连续;Ø 容易使信号之间发生串扰;Ø

CH9344公益评审报告

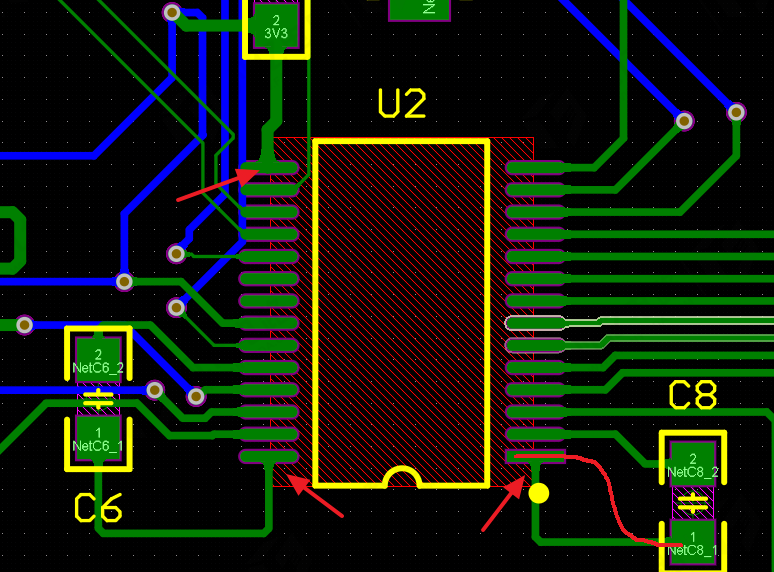

布线应从焊盘的长方向出线,避免从宽方向和四角出线。2. 布线尽量避免直角锐角布线,导致转角位置阻抗变化和造成信号反射;尽量避免线从其他器件中心穿过。3.建议顶底层整版覆地铜处理,器件就近打孔接地减短回流路径。4.电源稳压芯片输入电路应该先经

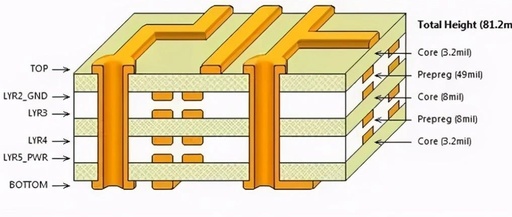

PCB的EMC设计考虑中,首先涉及的便是层的设置;单板的层数由电源、地的层数和信号层数组成;在产品的EMC设计中,除了元器件的选择和电路设计之外,良好的PCB设计也是一个非常重要的因素。PCB的EMC设计的关键,是尽可能减小回流面积,让回流路径按照我们设计的方向流动。而层的设计是PCB的基础,如何做

电流的路径是个环路。因此,每个电流信号有来肯定有回。要获得最佳的PCB设计,需要了解信号的回流的实际路径。电路的信号完整性和EMC性能,直接与电流环路形成的电感相关,而电感大小则主要与环路的面积相关。在做PCB设计时,比较容易忽略回流的实际路径,因为它不像信号路径(通常是微带线)那么形象。微带线的回

敷铜完整性的要求如图5-208与5-209所示,设计上保证主控下方敷铜的完整性及连续性,能够提供良好的信号回流路径,改善信号传输质量,提高产品的稳定性,同时也可以改善铜皮的散热性能。

差分对内等长凸起高度不能超过线距的两倍2.注意T点的间距要求,后期自己看视频在了解一下3.地网络需要就近打孔,缩短回流路径4.VREF的电源最少要加粗到15mil以上5.此处不满足载流6.注意差分走线要尽量耦合,满足差分间距要求,控好阻抗7

扫码关注

扫码关注