- 全部

- 默认排序

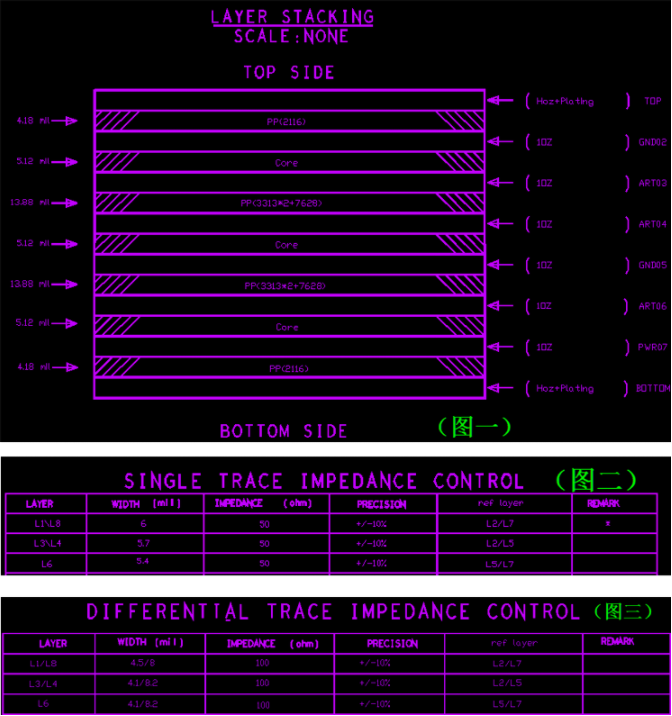

需要要做阻抗的信号线,应该严格按照叠层计算出来的线宽、线距来设置。比如射频信号(常规50R控制)、重要单端50R、差分90R、差分100R等信号线,通过叠层可计算出具体的线宽线距(下图示)。设计的线宽线距应该考虑所选PCB生产工厂的生产工艺

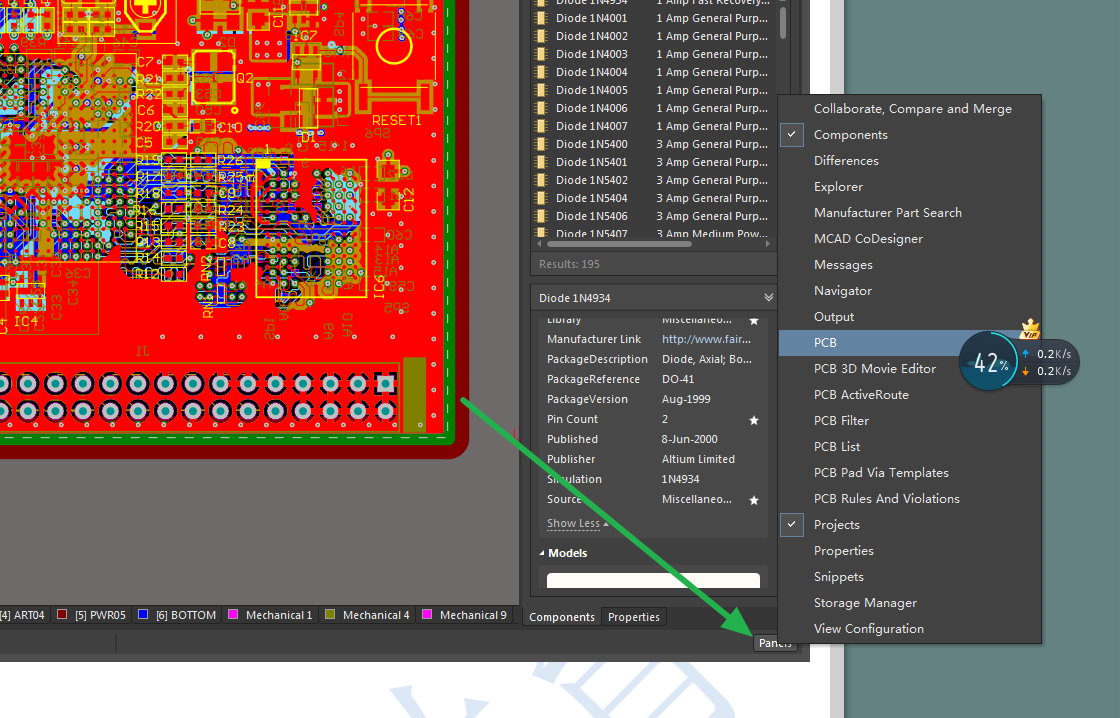

类是某种特定类型设计的逻辑集合,是将多个元素进行的一个集合。在AD软件汇总结构类将这个概念进行了进一步的层次上升,结构类是一种特殊形式的类,可以归纳一下成员: 网络类 元件类 板层类 焊盘类 From To 类 差分对类设计通道类 多边形铺铜类 其他的结构类

注意电源走线需要加粗,满足载流2.此处电源不满足载流,后期自己铺铜处理3.晶振需要包地处理,并在地线上打上地过孔4.注意232的升压电容走线需要加粗5.差分换层尽量在旁边打上一对回流地过孔6.USB差分对内等长误差5mil7.确认一下此处是

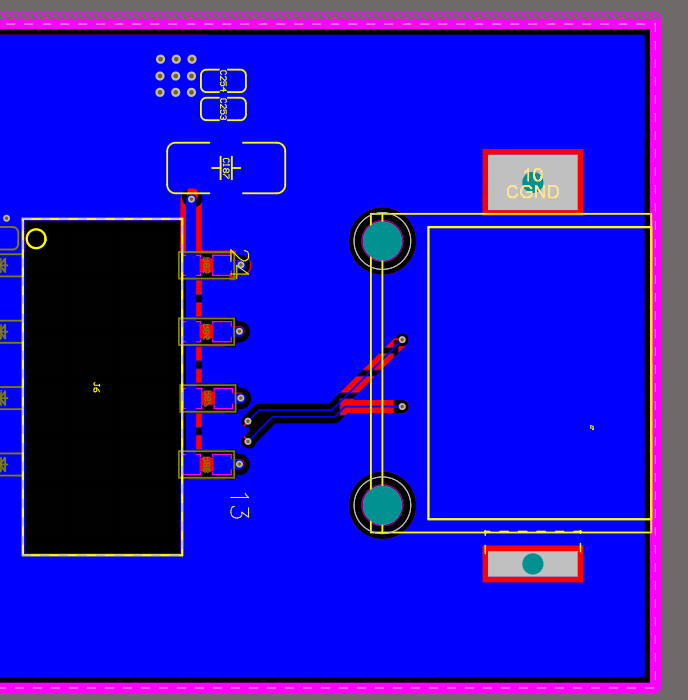

器件摆放太近,后期安装容易干涉2.与上述问题一样,期间这样,后期没法焊接,放不下3.网口差分需要进行对内等长,误差5mil4.网口除差分信号外,其他信号都需要加粗到20mil5.模拟信号一字型布局6.输出打孔要打在电容后面7.反馈要从电容后

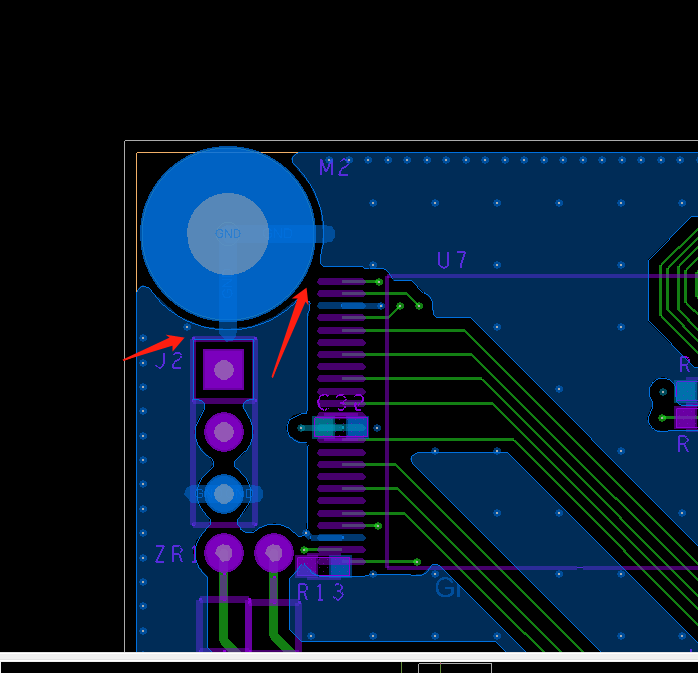

1、外壳地和GND底层铺铜没有分割2、外壳地与GND之间距离需要2mm以上3、跨接区域需要多打孔,外壳地这边也需要多打孔4、多处孤岛铜皮和尖岬铜皮5、差分布线不耦合6、差分换层需要旁边打过孔7、多余过孔没有删除8、电源走线需要加粗走线9、焊

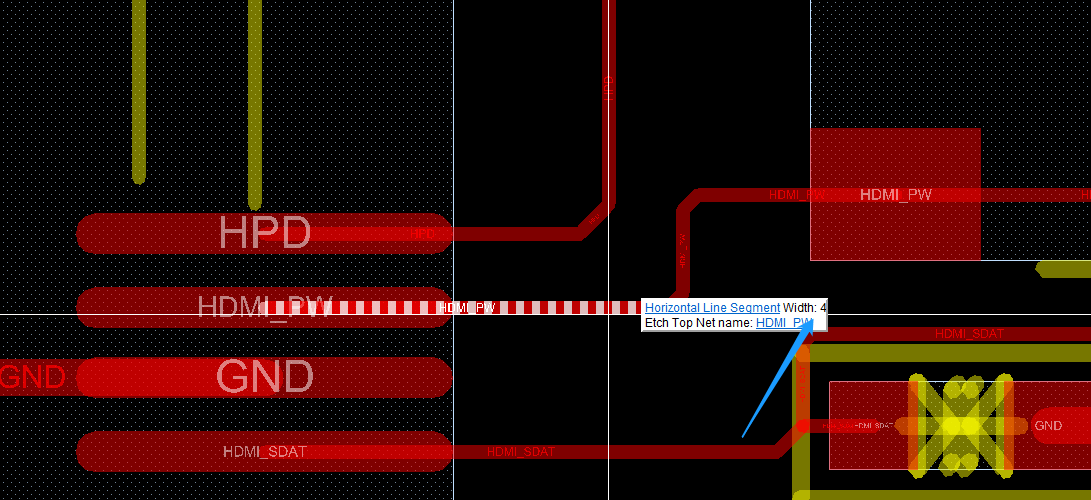

此处电源走线不满足载流,走线加粗或者铺铜处理2.滤波电容靠近管脚放置3.走线可以在优化一下,尽量不要有锐角4.HDMI差分对内等长误差5mil,对间误差10mil5.差分出线需要优化一下,走线尽量满足差分间距规则6.器件干涉7.滤波电容尽量

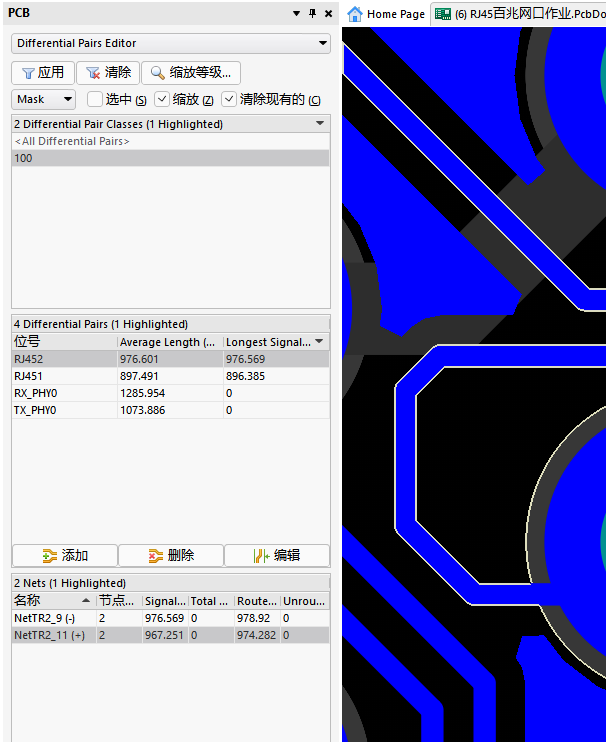

差分对内等长误差5mil2.未添加TR和RX的class3.包地要在地线上 打过孔4.器件干涉5.差分出线要尽量耦合6.时钟信号需要包地处理,并且打上地过孔7.pcb上存在两处开路以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需

扫码关注

扫码关注