- 全部

- 默认排序

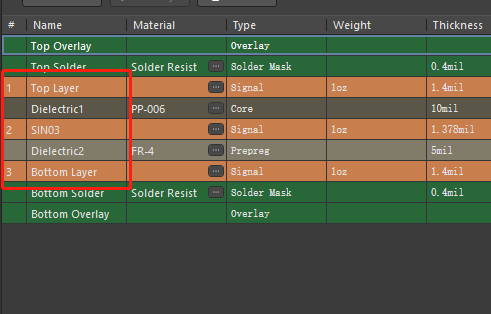

层叠一般都是双数,一般是4层,6层增加,高速信号都需要有完整的参考平面的2.差分走线注意要满足差分间距要求3.CC1和CC2属于重要信号管脚,走线需要加粗处理,ESD器件尽量靠近管脚摆放4.存在多处开路报错5.差分注意能顶层连通的就不用打孔

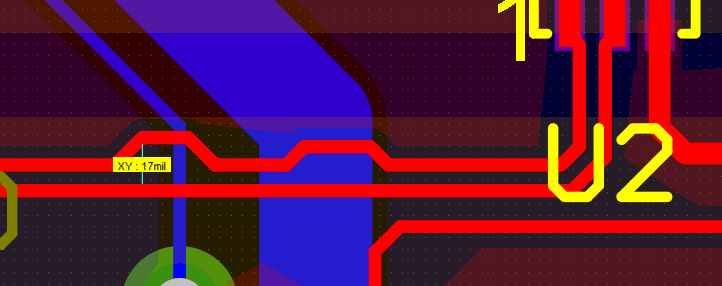

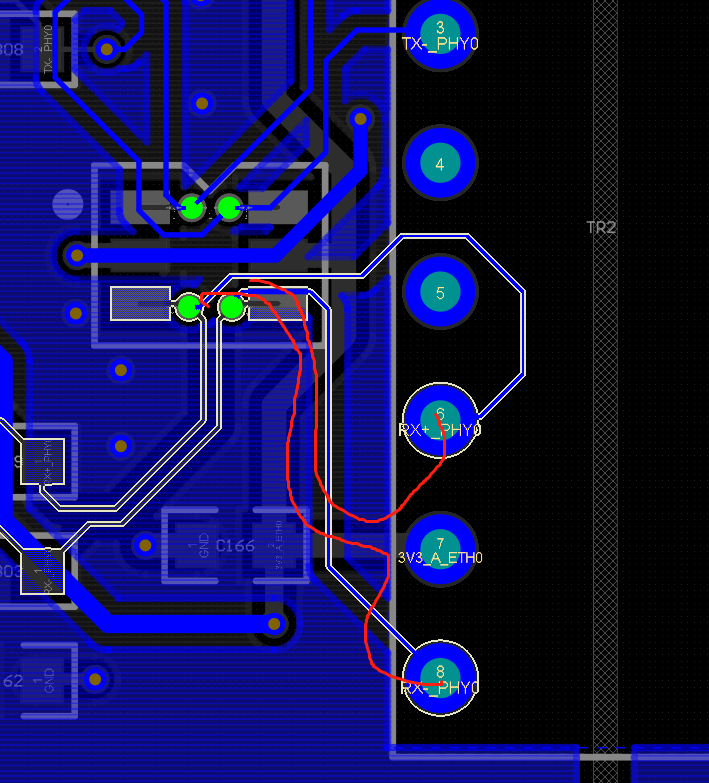

机壳地以及电源地没有正片铺铜处理也没有负片分割处理,注意地是需要处理的:变压器上除了差分信号,其他的加粗20MIL走线:电源层也并未处理电源 :TX RX信号之间用GND走线隔开:RX TX没有创建等长组进行等长:差分对内等长误差为5MIL

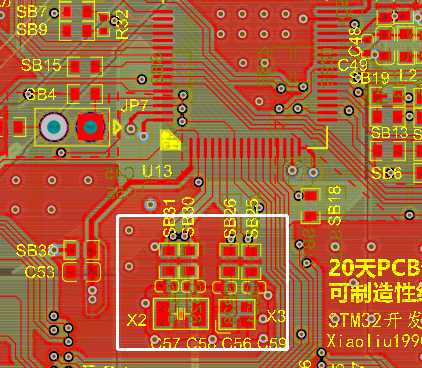

晶振可以在靠近管脚一些。差分锯齿等长不要大于两倍间距散热过孔正反都要开窗处理走线不满足3w间距这里输出要加粗处理电容按先大后小放置走线不要穿过电容电阻

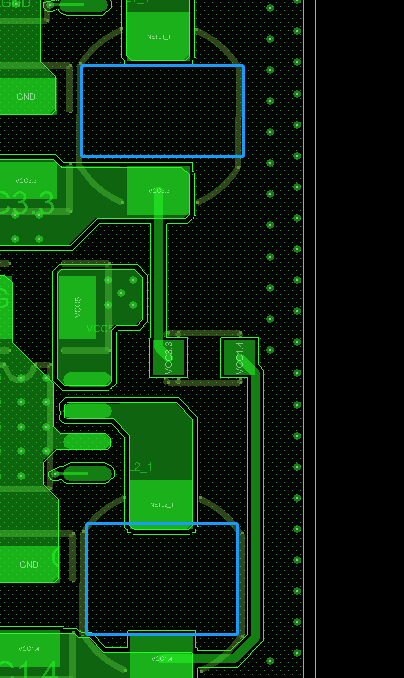

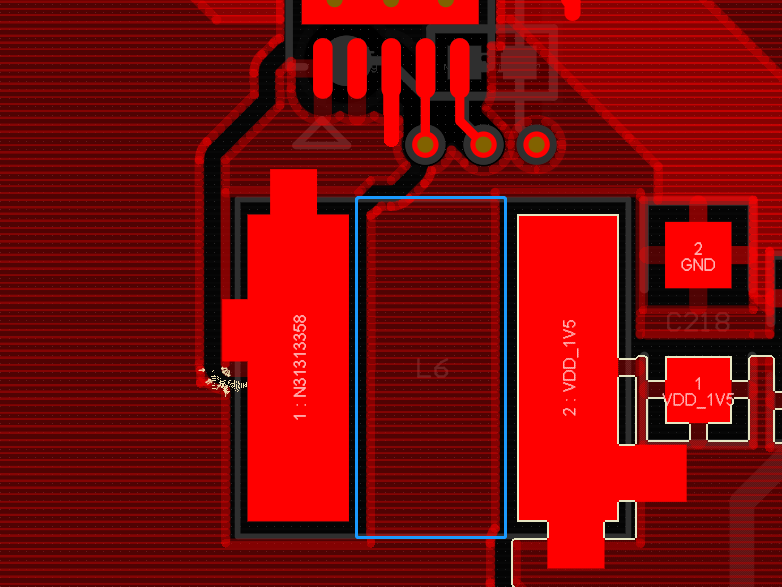

电感所在层测内部需要挖空处理2.地分割间距最少控制1mm以上,有跨接器件的地方不满足可以忽略,其他地方尽量一致3.除差分线外,其他的都需要加粗到20mil4.注意过孔尽量不要上焊盘5.注意等长线之间需要满足3W6.地址线也需要添加等长组进行

电感所在层的内部需要挖空处理2.差分线处理不当,锯齿状等长不能超过线距的两倍3.走线未连接到过孔中心,存在开路4.VREF的线宽需要加粗到15mil以上5.焊盘需要开窗处理6.器件干涉7.此处出线载流瓶颈,自己加宽一下铜皮以上评审报告来源于

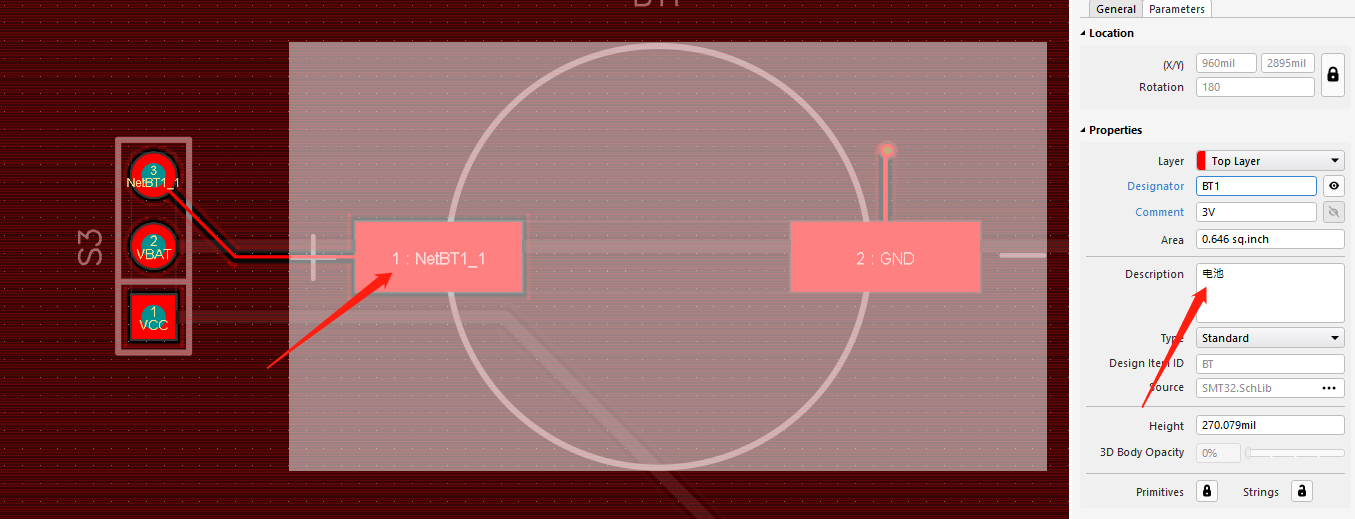

地缘信号走线需要加粗处理,尽量满足载流2.SD卡需要靠近板框放置3.SD卡信号线需要进行等长处理,误差300mil4.焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊5.晶振需要走内差分,并包地处理,在地线上均匀的打上地过孔

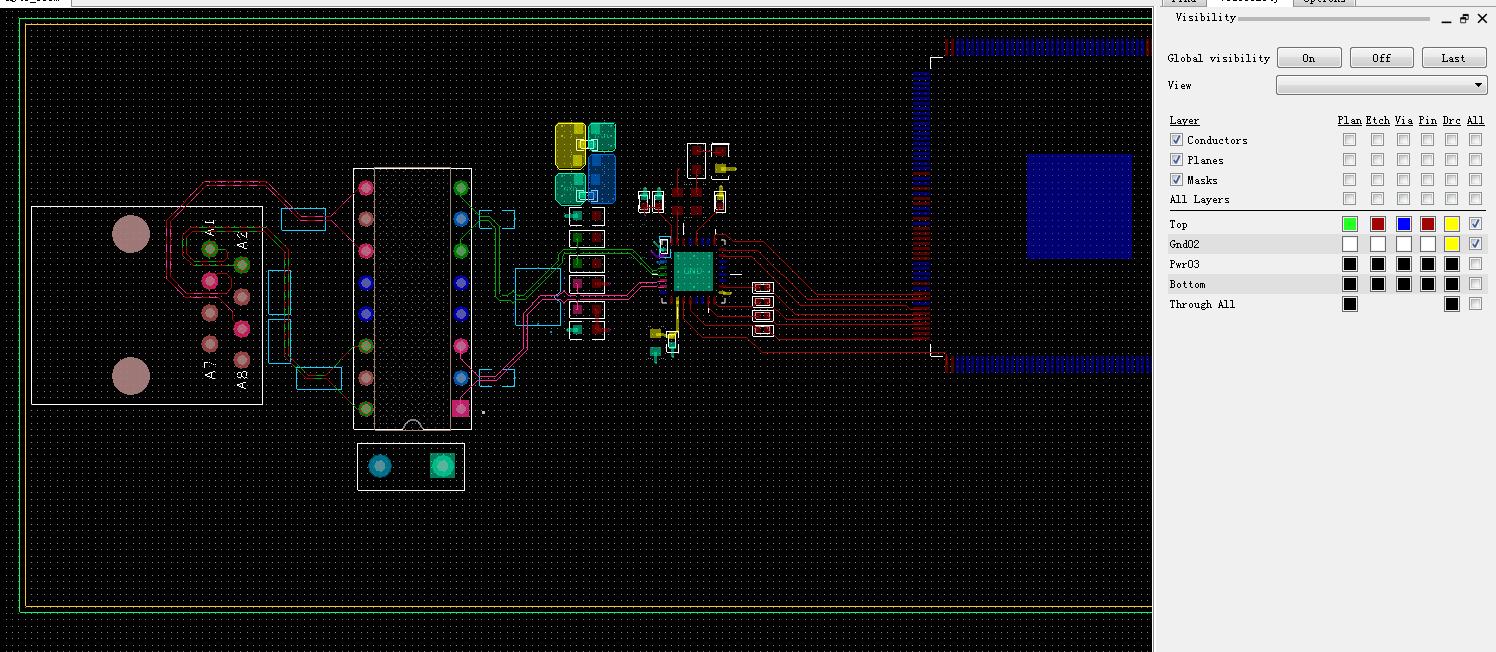

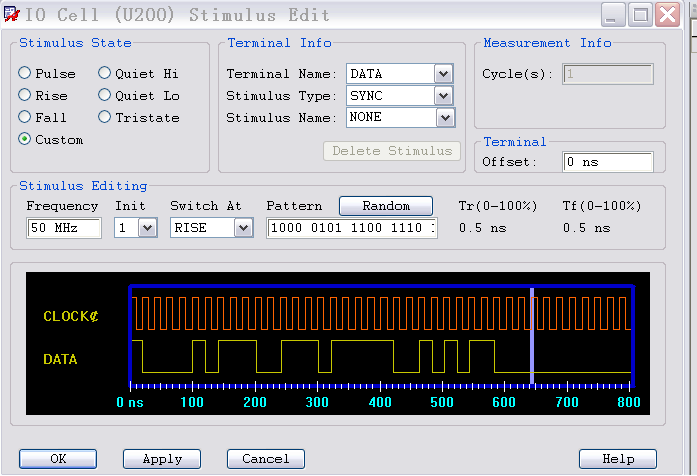

SI分析的前期准备完成之后,就可以进行信号完整性分析了,执行Analyze/SI EMI Sim/Probe命令,然后选择需要进行SI分析的网络或者差分对(模型分配中必须设置好差分对),如下图所示:

差分线要按阻抗线宽线距要求耦合走线网口到芯片的差分都需要优化,后期自己好好理解差分,然后走线需要调整一下2.器件摆放尽量中心对齐处理3.走线需要优化一下,不要有锐角4.TX分组错误5.注意等长蛇形走线尽量45度,不要直角6.除了散热过孔,其

提起RS485总线,很多电子人不会陌生,RS485总线是一种广泛应用于工业自动化、楼宇自动化、智能家居等领域的数据通信协议。它采用差分信号传输,具有抗干扰能力强、传输距离远、接口简单等优点。今天我们来聊聊RS485总线的五种切换方向。1、单

扫码关注

扫码关注