- 全部

- 默认排序

Cannot load symbol 'MPXC-P5-L15W6_4-HP2_55' because WARNING(SPMHUT-127): Could not find padstack T_CIR86_86_56. due to ERROR(SPMHDB-274): Unable

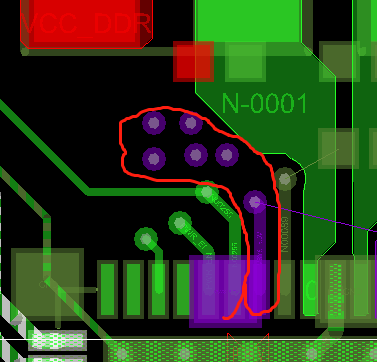

地分割间距要保证2mm,有器件的地方可以不满足2.网口除差分信号外,其他的都需要加粗到20mil3.晶振需要包地处理,并在地线上4.BGA里面的铜皮建议挖空处理5.焊盘到孔的间距过近,建议6mil,后期自己优化一下以上评审报告来源于凡亿教育

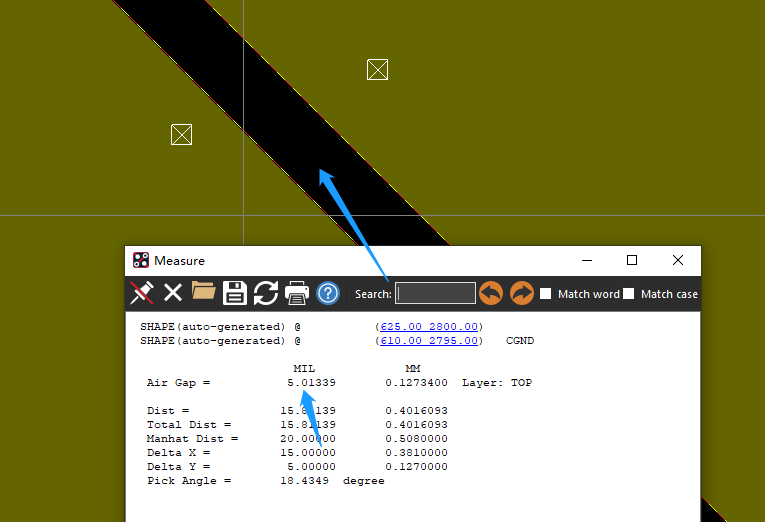

在电子工程师的日常工作中,长时间面对PCB设计软件是很容易带来眼睛疲劳等问题,为了提高工作效率,很多工程师选择将软件界面切换为暗黑模式,该模式提供了更舒适的视觉体验,特别是在低光环境下或长时间使用的情况下,那么在ALLEGRO 17.4版本

电源打了几个孔需要再顶层铺铜进行连接,或者走线连接2.电源在底层铺一块铜皮进行连接3.这个电源走一根20mil的线就足够了4.地网络直接打孔在底层铺整版铜,不用进行走线连接5.过孔没有网络6.器件摆放干涉,摆放器件时最好把丝印层打开以上评审

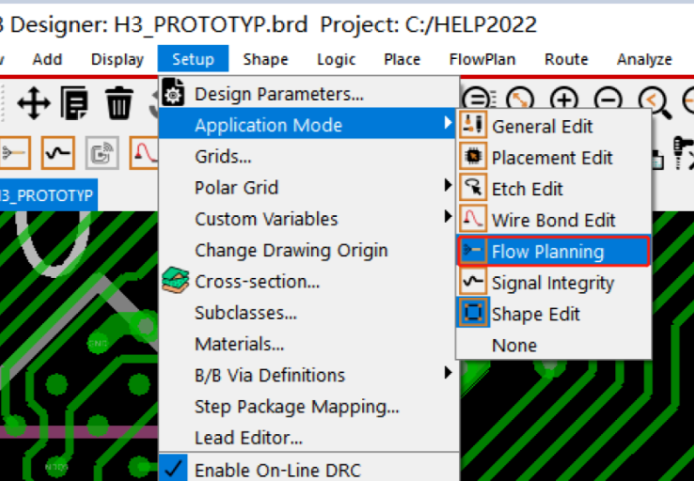

GRE是Global Route Environment的缩写,中文意思为全局布线环境,运用具备阶层化意识的全面绕线引擎与图形式互连流程规划程序。通GRE技术在短时间就可以开发出包含众多互连总线与芯片引脚数的复杂且高速的设计组件。此外,运用

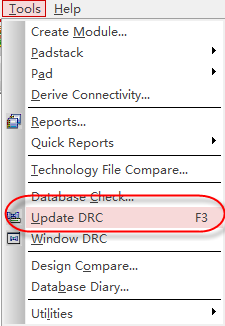

答:在使用动态铜皮的时候,会出现对铜皮进行Update to Smooth完了,还存在Out of date shapes的现象,如图6-332所示:

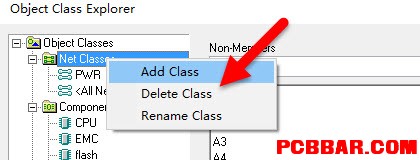

答:我们在Allegro中进行设计的时候,总会遇到这样的问题,创建类的时候,可供选择的选项太多,这里我们对这些不同的类做一个说明:

扫码关注

扫码关注