- 全部

- 默认排序

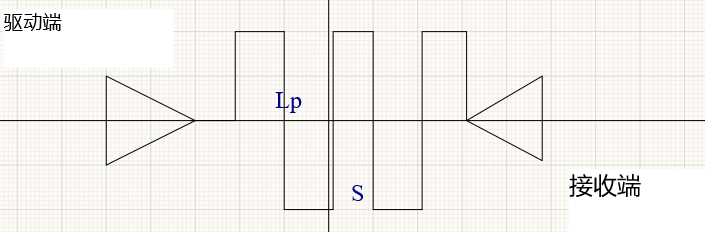

在PCB设计中,蛇形等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多条数据信号基于同一个时钟采样,每个时钟周期可能要采样两次甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序影响比重越来越大,为了保证在数据采样点能正确采集所有信号的值,就必须对信号传输延迟进行控制。

PCB上的任何一条走线在通过高频信号的情况下都会对该信号造成时延时,蛇形走线的主要作用是补偿“同一组相关"信号线中延时较小的部分,这些部分通常是没有或比其它信号少通过另外的逻辑处理;最典型的就是时钟线,通常它不需经过任何其它逻辑处理,因而其延时会小于其它相关信号。

蛇形走线是PCB布局布线中常用的特殊走线之一,也是小白初入PCB设计中的难点之一,今天将以蛇形走线为主,重点分享它的技巧和用法,希望对小伙伴们有所帮助。蛇形走线外文名为serpentine,是PCB布局布线的一种特殊走线方式,主要目的是为了

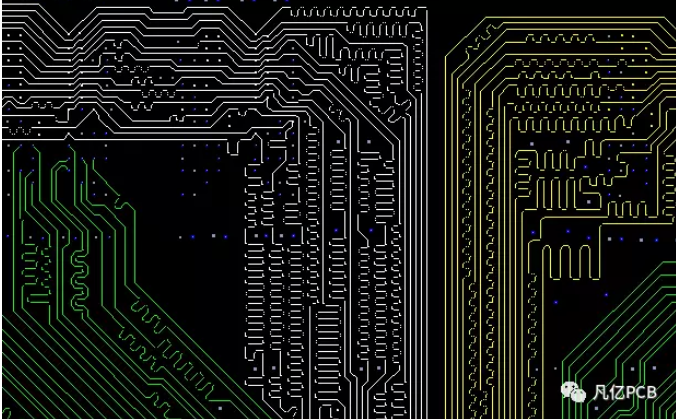

至于USB,SATA,PCIE等串行信号,并没有上述并行总线的时钟概念,其时钟是隐含在串行数据中的。数据发送方时钟包含在数据中发出,数据接收方通过接受到的数据恢复出时钟信号。这类串行总线没有上述并行总线等长布线的概念。但因为这些串行信号都采用差分信号,为了保证差分信号的信号质量,对差分信号对的布线一般会要求等长且按总线规范的要求进行阻抗匹配的控制

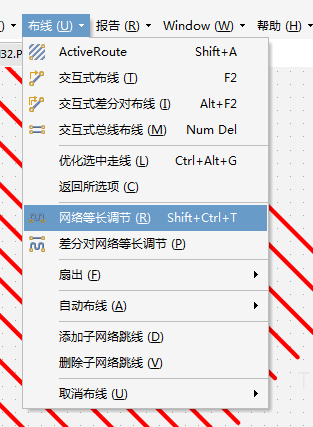

PADS蛇形等长处理

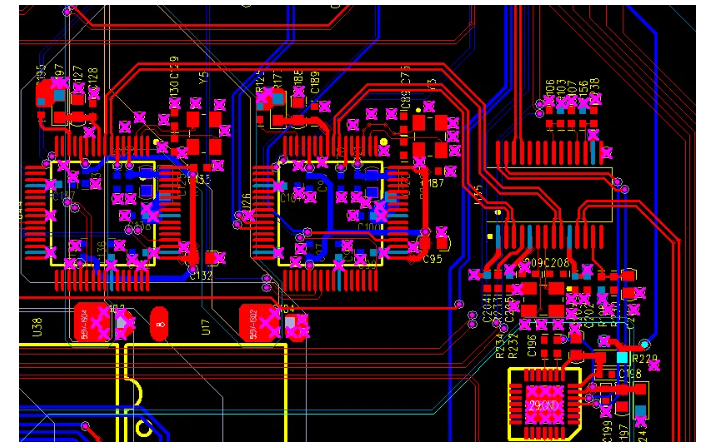

在做PCB设计时,为了满足某一组所有信号线的总长度满足在一个公差范围内,通常要使用蛇形走线将总长度较短的信号线绕到与组内最长的信号线长度公差范围内,这个用蛇形走线绕长信号线的处理过程,就是俗称的PCB信号等长处理。如图6-59示。图6-59

PCB设计信号等长分析

在做PCB设计时,为了满足某一组所有信号线的总长度满足在一个公差范围内,通常要使用蛇形走线将总长度较短的信号线绕到与组内最长的信号线长度公差范围内,这个用蛇形走线绕长信号线的处理过程,就是我们俗称的PCB信号等长处理。

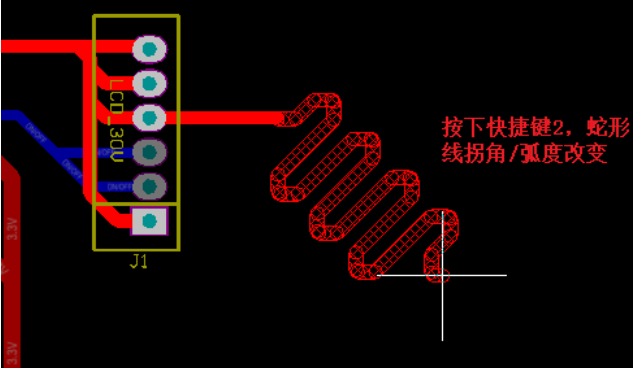

PCB设计,遇到差分线,需要做等长设计时,该怎么操作呢?在做走线等长设计的时候,我一般都是采用让走线进入蛇形走线模式,然后走出蛇形线来快速完成等长设计。

全站最新内容推荐

- 1常规变压器耦合型自激调频式开关电源电路分析讲解

- 2低压MOS在多电平逆变器上的应用-REASUNOS瑞森半导体

- 3走进电子元件,了解双稳态触发器

- 4模拟电路太难读?有没有可能是你不会看!

- 5要使用电烙铁,应该注意什么?

- 6硬件设计:4.10 通过这个实验,你会深刻认识到电感滤波与电容滤波电路的区别(为什么电容型滤波电路不能用在大电流环境)

- 7硬件设计:4.8-4.9 电感教程_滤波电路_低通滤波电路为什么分为电容型和电感型

- 8硬件设计:4.7电感教程_为什么有些开关电源在上电时会过压_怎么解决

- 9硬件设计:4.6 电感教程_5V电压升至1万V电压的工作原理

- 10硬件设计:4.5 电感教程之开关电源教程(boost型)_重新认识电感的重要性

扫码关注

扫码关注