- 全部

- 默认排序

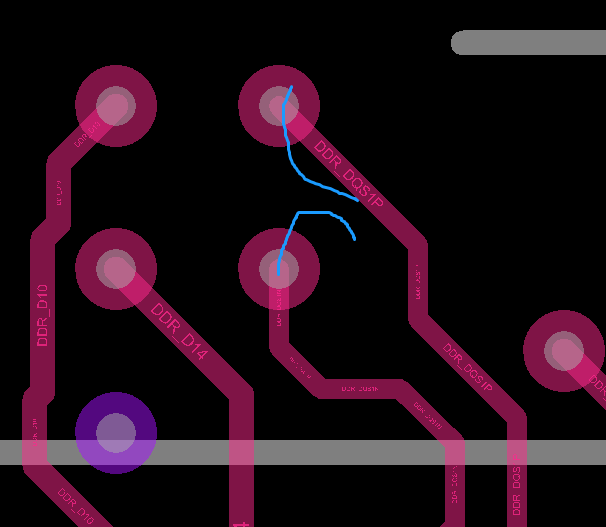

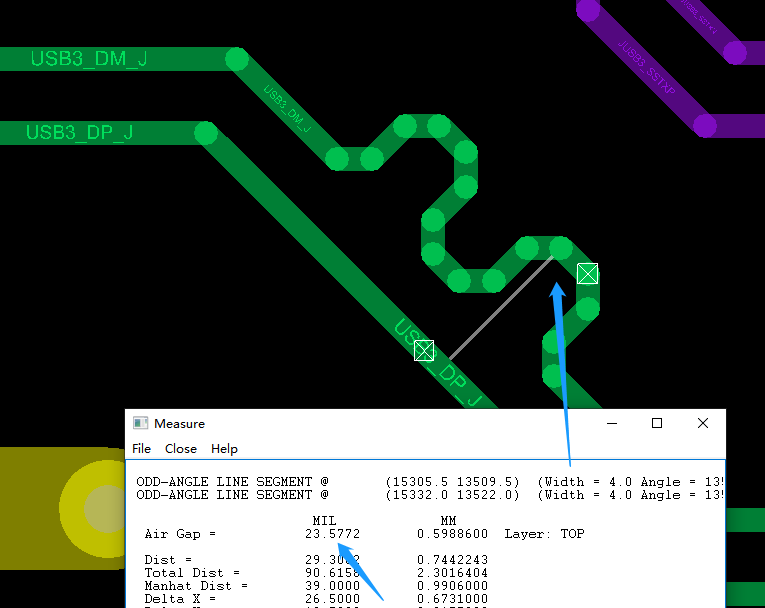

差分走线要耦合出线2.差分对内等长凸起高度不能超过线距的两倍3.器件摆放干涉,后期自己调整一下放底层4.器件摆放太近5.滤波电容尽量保证一个管脚一个,原理图不够可以自己添加6.过孔不要上焊盘7.差分出线要尽量耦合以上评审报告来源于凡亿教育9

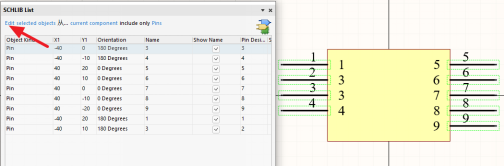

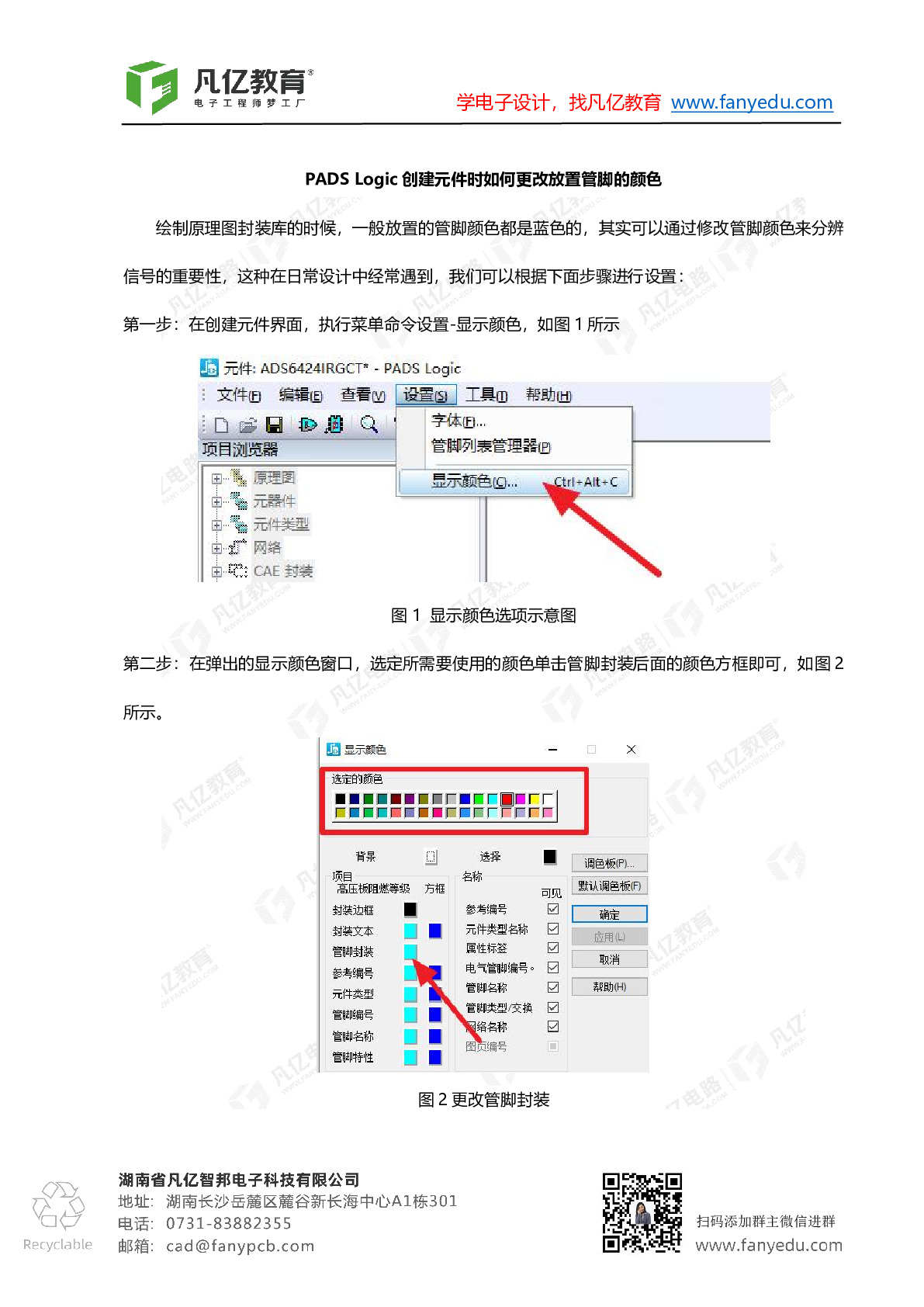

答:针对于管脚数目比较多的IC类元器件,可以先把全部的管脚数目放置出来,然后进行属性的统一修改。操作的步骤如下:

2、 广州PCB培训元器件封装 是实际元器件焊接到PCB板时的焊接位置与焊接形状,包括了实际元器件的外形尺寸,所占空间位置,各管脚之间的间距等。 元器件封装是一个空间的功能,对于不同的元器件可以有相同的封装,同样相同功能的元器件可以有不同的封装。因此在制作PCB板时必须同时知道元器件的名称和封装形式。 (1) 元器件封装分类

从PADS转过来的PCB到allegro中, 不显示Pin Number ,但是查询看是有pin number的,啥原因?

锯齿状等长不能超过线距的两倍很多差分都存在相同的问题,后期自己修改一下2.焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊3.CC1属于重要信号,需要加粗处理4.ESD器件尽量靠近座子管脚放置5.差分出线要尽量耦合6.器件摆

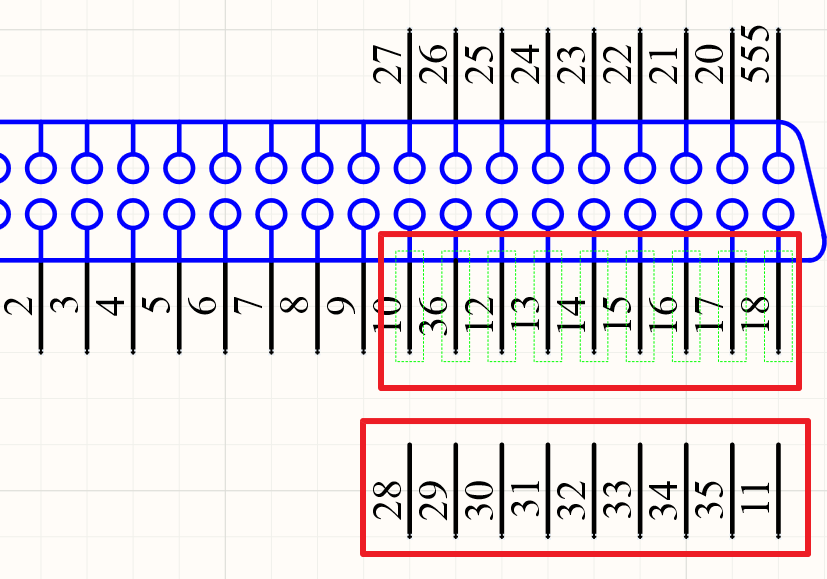

在绘制原理图原器件封装的时候,制作一个管脚特别多的原理图原器件封装。需要一个一个的模块功能分开,功能管脚需要放置到一块。运用快捷键快速的交换管脚可以省去大量的时间。以如下一个连接器为例,当我们想把框选中的这部分管脚移动到其它地方去的时候,我

在logic软件当中制作CAE封装,对于管脚少的器件可以手动的输入管脚名称和编号,但对于一些管脚特别多的器件可以利用导入CSV文件的方式,一次性把管脚信息全部导入,节省了我们制作封装的时间。

扫码关注

扫码关注