- 全部

- 默认排序

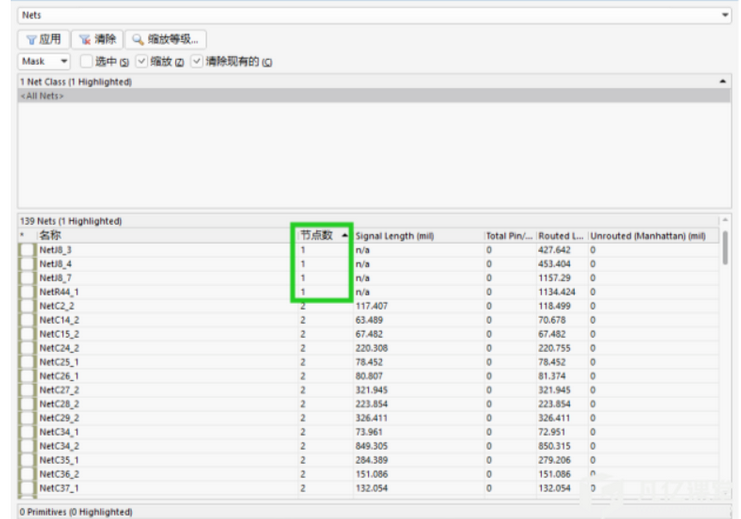

单端网络在PCB设计中是一个非常重要的概念,它是指信号在电路中传输的一种方式,但有很多电子小白没听说过这个专业术语,所以本文凡小亿将带领小伙伴们来了解这个单端网络,以及查看方法。一般来说,单端网络是指信号在电路中传输时只有一根线,即信号线,

电路板上的线路漏电是一种常见的问题,可能导致设备故障、安全隐患甚至损坏,所以如果发现电路板出现线路漏电,一定要排查找到事发原因,然后解决掉。下面将给出电路板上线路漏电的原因、检查及解决方法。1、线路漏电原因分析线路漏电的主要原因基本上可归纳

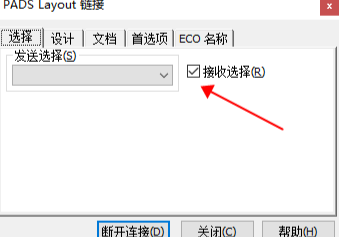

布局时一般需要与原理图同步,进行协作处理,提高布局效率。可同时打开Logic格式原理图与Layout格式PCB文件,在Logic内执行“工具-Pads Layout”命令,然后设置“选择”界面,与原理图同步的PCB须检查,以防文件不对应,一

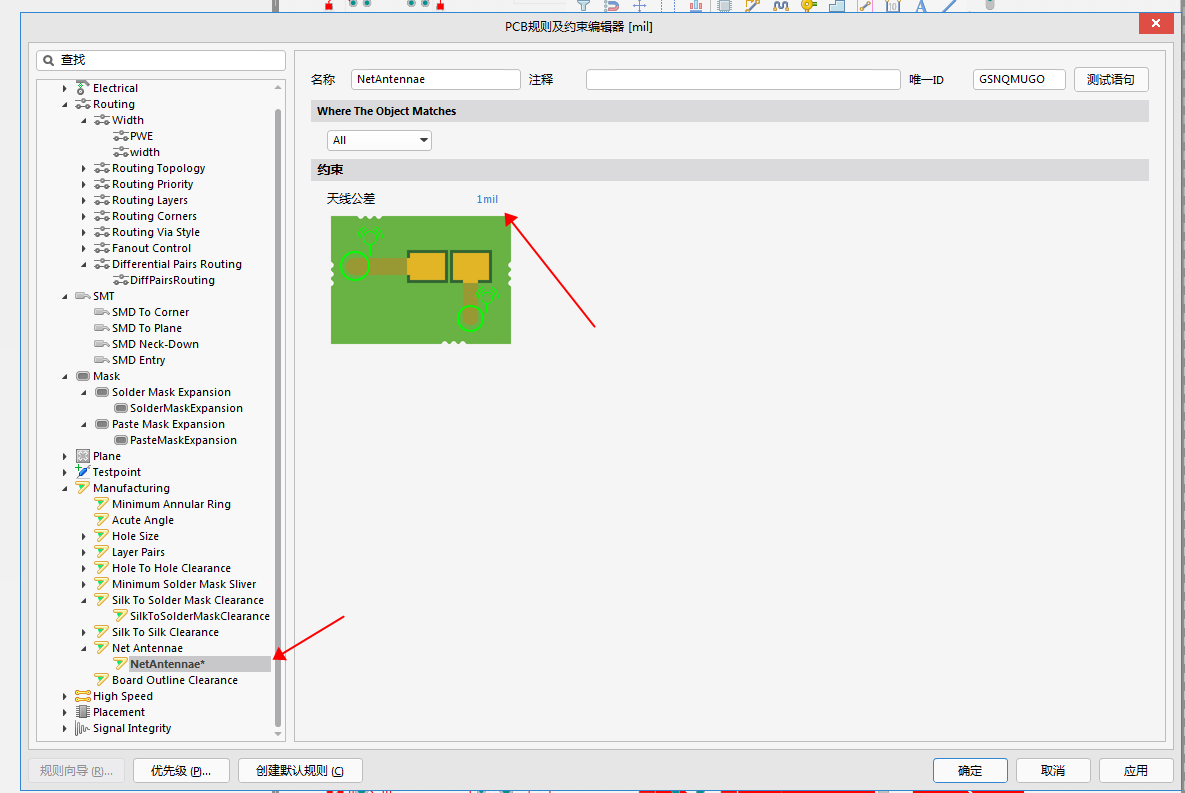

虽然可以对走线进行一些优化处理,但是考虑到还要人工进行布线处理,难免会对走线的一些线头有遗漏,这种线头简称Stub线头。Stub线头在信号传输过程中相当于一跟“天线”,不断地接受或发射电磁信号,特别是高速的时候,容易给走线导入串扰,所以有必要对Stub线头进行检查,并在设计中进行删除处理。

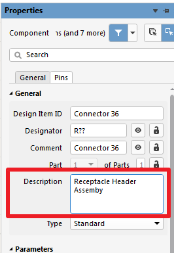

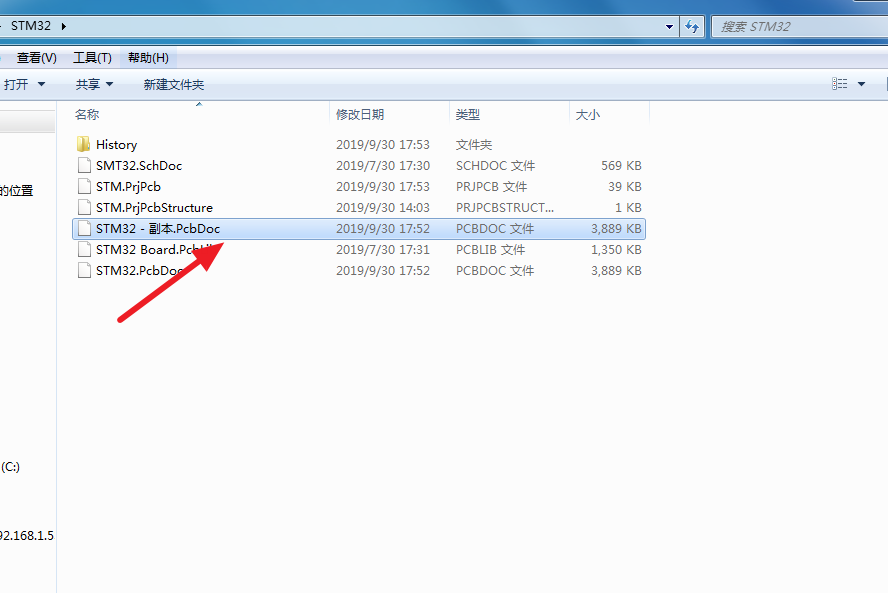

我们在进行PCB设计时,在连线走线的时候,会经常出现这么两种情况:1.走线连接到焊盘上时,我们以为自己已经连接到了焊盘中心点上,早已连接上了,其实没有。那么,这个对于我们后期会造成虚焊,而且这一项有时DRC也检查不出来。所有为了减少我们不必要的损失,就来讲一下这项常用的方法。2.走线跟走线连接的时候,以为是连接上了,其实也是没有连接上来,会有开路的现象。

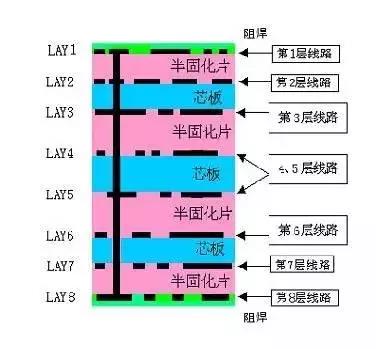

PCB制板全过程详解

PCB制作第一步是整理并检查PCB布局(Layout)。PCB制作工厂收到PCB设计公司的CAD文件,由于每个CAD软件都有自己独特的文件格式,所以PCB工厂会转化为一个统一的格式——Extended Gerber RS-274X 或者 Gerber X2。然后工厂的工程师会检查PCB布局是否符合制作工艺,有没有什么缺陷等问题。

一直以来很多工程师都想进入中国大厂里工作,而Allegro作为中国大厂使用率最高的EDA软件,更是这些工程师的重点学习软件,但在学习过程中遇见器件被锁定,通过多种方法仍然无法解决,该怎么办?1、检查设计规则和限制检查设计规则和限制文件,确保

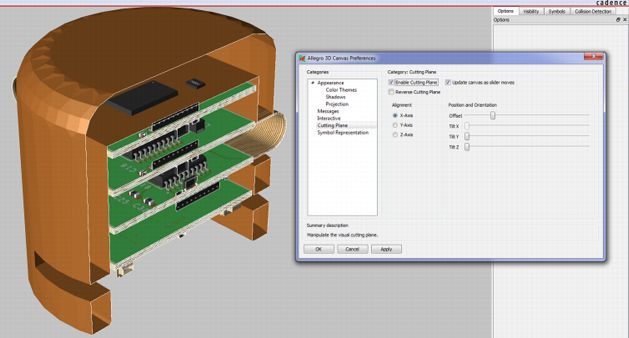

各位小伙伴大家好,Cadence Allegro 软件一直以来,都能够支持3D PCB的模型制作和预览功能,但是一直以来立体感和视角的效果都不够理想。为了能够给工程师更加直观的PCB立体设计体验,Cadence做了很大的努力。从Allegro 17.2开始,Allegro已经能够支持立体的三维PCB设计和交互预览功能,能够让工程师在三维模式下进行交互Layout。今天我们将来一起体验学下逼真的3D功能吧。

扫码关注

扫码关注