10.11 走线与覆铜优化

处理完连通性之后,需要对走线和覆铜进行优化,一般分为以下几个方面。

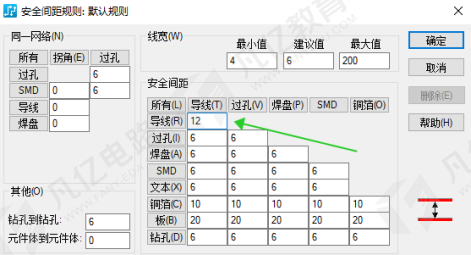

(1)走线间距满足3W原则。在走线时有时不注意,走线和走线太近,容易引起走线之间的串扰。处理完连通性之后,可以设置一个线与线间距的规则去协助检查,如图10-60所示。

10-60 布线规则设置

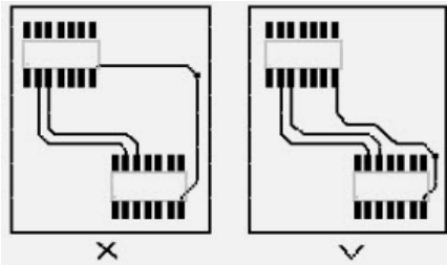

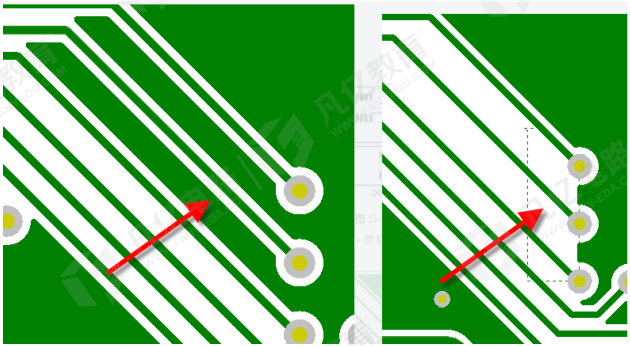

(2)减小信号环路面积。如图10-61所示,走线经常会包裹一个很大的环路,环路会造成对外辐射的面积增大,同样吸收辐射的面积也增大,走线优化的时候需要进行优化处理,减小环路面积,一般是按快捷键“Shift+S”单层显示之后人工检查。

10-61 布线环路检查

(3)修铜。主要是对一些电路瓶颈的地方进行修整,还有就是尖岬铜皮的删除,一般通过放置Cutout进行删除,如图10-62所示。

图10-62 铜皮处理

扫码关注

扫码关注