- 全部

- 默认排序

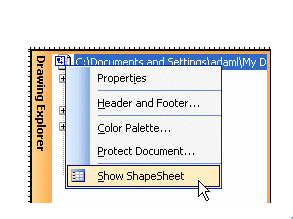

答:orcad创建封装库时,放置管脚的Shape的含义是管脚的长度以及一些特殊含义,其表示的含义解释如下:Clock:时钟信号,管脚的长度是标准长度;Dot:低电平有效信号,管脚的长度是标准长度;Dot-Clock:低电平有效的时钟信号,管脚的长度是标准长度;Line:普通信号,管脚的长度是标准长度;Short:普通信号,管脚的长度比标准的长度要短一些;Short Clock:时钟信号,管脚的长度比标准的长度要短一些;Short Dot:低电平有效信号,管脚的长度比标准的长度要短一些;Short

在PCB布局布线时,很多新人工程师可能会听见这种说法,类似于“PCB蛇形线越多,就显得板子高级”,虽然蛇形线可以调整长度,满足特定的时序要求,平衡线路间的长度差异,但这种说法在大多数情况下是错误的!1、尽量减少蛇形线的使用蛇形线虽然能解决部

1、MD5概念MD5信息摘要算法(MD5 Message-Digest Algorithm),一种被广泛使用的密码散列函数,可以产生出一个128位(16字节)的散列值(hash value),用于确保信息传输完整一致。输入任意长度的数据经过处理,输出都是128位的信息(数字指纹)。不同的输入得到的不

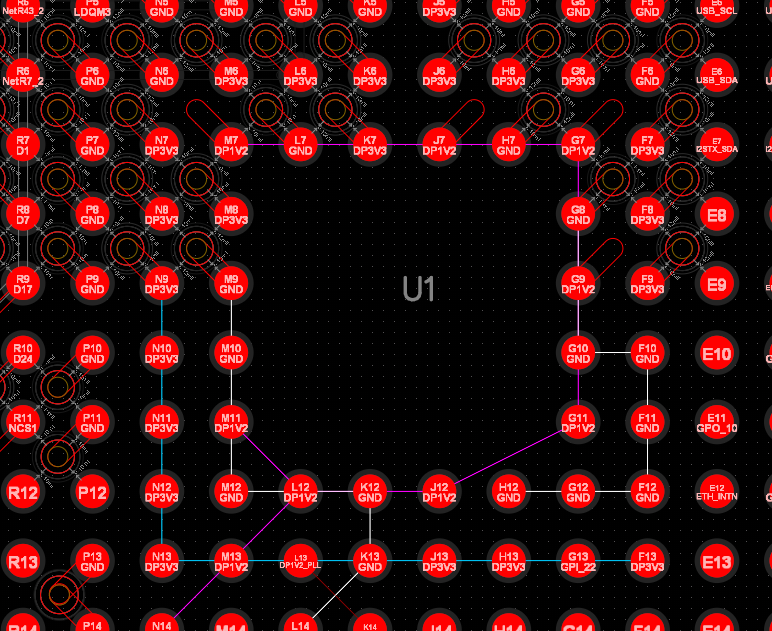

GND跟电源网路都没有处理:地址线都有及个别的没有跟BGA内的扇孔连接:等长线的GAP尽量大于等于3W,不要太短了:数据线一组走线尽量紧凑点:看下是否存在间距报错:等长线之间要满足3W间距原则:上述一致问题,等长线GAP满足下3W长度:间距

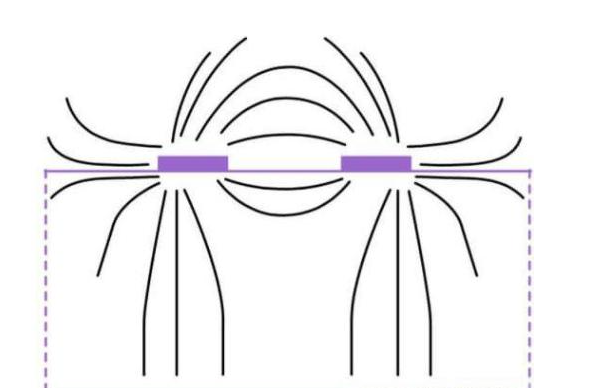

答:降低串扰的方法有如下几种:增加信号路径之间的间距、用平面作为返回路径、使耦合长度尽量短、在带状线层布线、减小信号路径的特性阻抗、使用介电常数较低的叠层、在封装和接插件中不要共用返回引脚、使用两端和整条线上有短路过孔的防护布线,更多关于PCB中降低串扰的处理方法,可以到本书学习论坛“PCB联盟网”免费下载学习。

本视频的讲解主要是讲解关于我们如何进行高亮我们的对应的网络,以及如何高亮我们的对应的其它网络,以及如何测量我们的此网络的线段的长度的一个小技巧的操作过程。

答:高速信号、低速信号的区分取决于以下两个因素:信号的有效频率F;信号走线的有效长度U。一般来说,信号的有效频率F约等于信号频率的5倍,信号走线的有效长度等于U=(0.35/F)/D,其中D是PCB上的走线延迟,在FR4的材质中D约等于180,得出的结论就是在信号走线的长度小于有效长度的1/6,信号为低速信号;反之,信号为高速信号。所以我们判定信号是否为高速、低速信号的步骤如下:Ø 获取信号的有效频率与信号走线的长度;Ø 计算出信号走线的有效长度;Ø 比较信号长度与

扫码关注

扫码关注