- 全部

- 默认排序

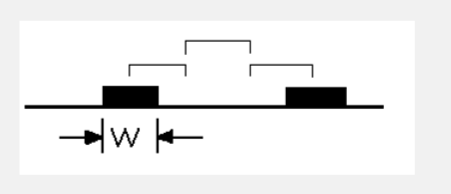

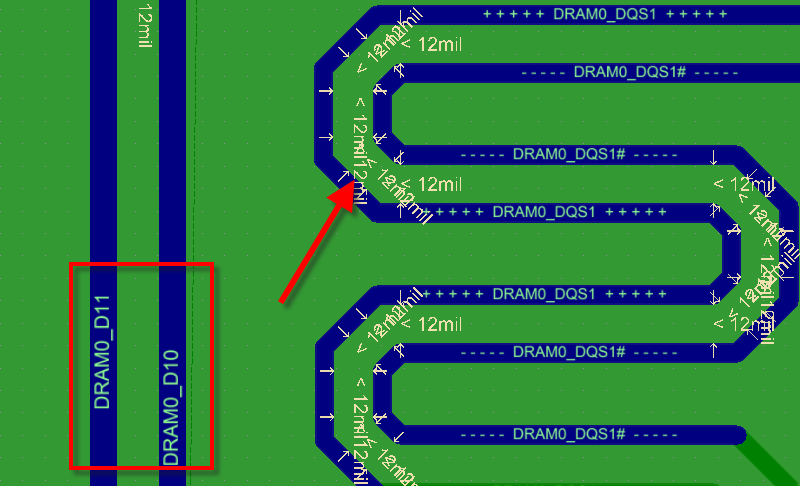

答:为了信号走线的质量,不产生串扰,我们保持信号走线与信号走线之间的间距为3倍线宽,这个间距指的是走线的中心到中心的间距,因为我们的线宽英文是width,所以这个规则我们通常就叫做3W原则。当我们的走线的中心间距不少于3倍线宽时,可以保证70%的线间电场不互相干扰,如果信号需要达到98%的线间电场不互相干扰,可以使用10W规则。3W原则是一种设计者无须其他设计技术就可以遵守PCB布局的原则。但这种设计方法占用了很多面积,可能会使布线更加困难。使用3W原则的基本出发点是使走线间的耦合最小。这种原则

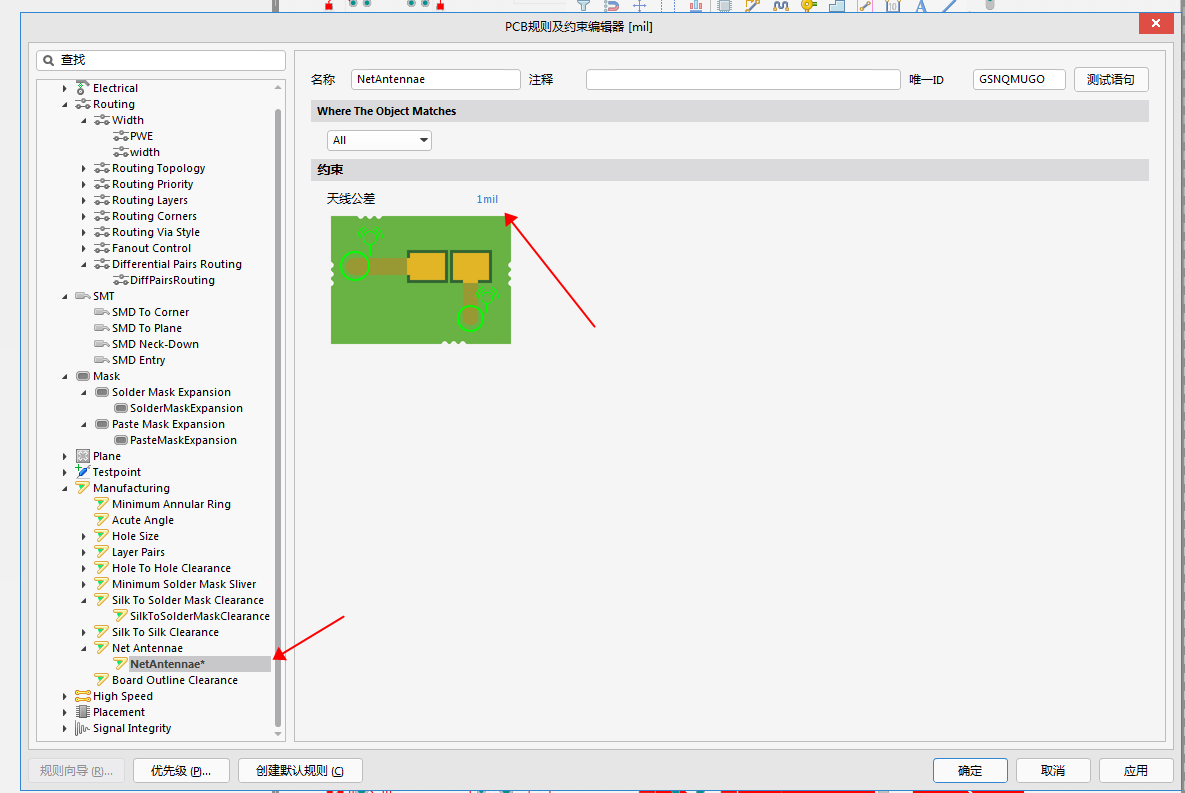

虽然可以对走线进行一些优化处理,但是考虑到还要人工进行布线处理,难免会对走线的一些线头有遗漏,这种线头简称Stub线头。Stub线头在信号传输过程中相当于一跟“天线”,不断地接受或发射电磁信号,特别是高速的时候,容易给走线导入串扰,所以有必要对Stub线头进行检查,并在设计中进行删除处理。

随着高频高速电子产品的快速发展,信号传输过程更容易出现反射、串扰等信号完整性问题,且频率越高、传输速率越快,信号损耗越严重,如何降低信号在传输过程中的损耗、保证信号完整性是高频高速PCB发展中的巨大挑战。在高速PCB设计中,阻抗匹配显得尤为

答:我们PCB中的信号都是阻抗线,是有参考的平面层。但是由于PCB设计过程中,电源平面的分割或者是地平面的分割,会导致平面的不完整,这样,信号走线的时候,它的参考平面就会出现从一个电源面跨接到另一个电源面,这种现象我们就叫做信号跨分割。跨分割的现象如图1-52所示。跨分割,对于低速信号,可能没有什么关系,但是在高速数字信号系统中,高速信号是以参考平面作为返回路径,就是回流路径。当参考平面不完整的时候,会出现如下影响:Ø 会导致走线的的阻抗不连续;Ø 容易使信号之间发生串扰;Ø

在高频PCB设计中,如何降低串扰问题的影响,是很多电子工程师必须考虑的首要问题,串扰,即信号线之间的互相干扰,可能导致信号失真、误码率上升,从而影响整个电路的性能和稳定性,那么如何从布局布线方面入手?1、利用地线隔离在布线空间允许的条件下,

随着半导体集成度越来越高,PCB层间的串扰问题愈发严重,虽然很多电子工程师通过3W规则来解决串扰,但你知道吗?还有很多方法可以抑制PCB板的串扰问题。串扰CrossTalk)是指PCB上不同网络之间因较长的平行布线引起的相互干扰,主要是由于

为了尽量减小单板设计的串扰问题,PCB设计完成之后一般要对线间距3W规则进行一次规则检查。一般的处理方法是直接设置线与线的间距规则,但是这种方法的一个弊端是差分线间距(间距设置大小不满足3W规则的设置)也会DRC报错,产生很多DRC报告,难以分辨

5分钟带你了解串扰

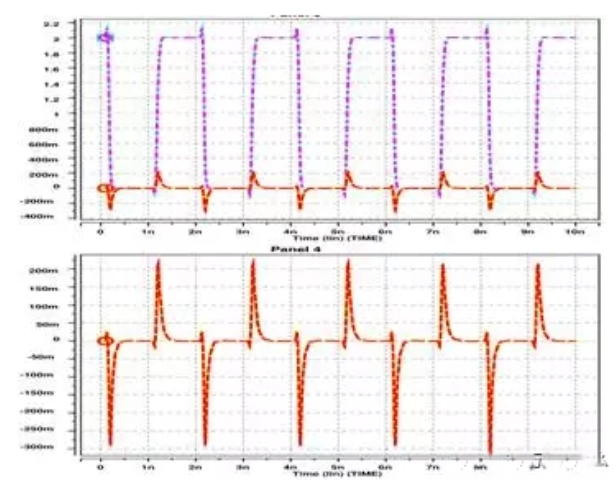

在射频电路研究学习的过程中,相信大家都遇到过在电路中信号频率的变高、边沿变陡、电路板的尺寸变小、布线的密度变大等问题,这些几乎是不可避免的问题。这种影响信号完整性的问题叫做串扰,在电路计中普遍存在,有可能出现在芯片、PCB板、连接器、芯片封

之前聊了下影响信号完整性(SI)的两个因素,即反射和串扰,接下来我们将聊聊过冲下冲、振铃、信号延迟等,希望对小伙伴们有所帮助,若是想看上篇可点击右侧链接《一文教你看懂信号完整性(SI)(上)》。3、过冲(Overshoot)与下冲(Unde

扫码关注

扫码关注