- 全部

- 默认排序

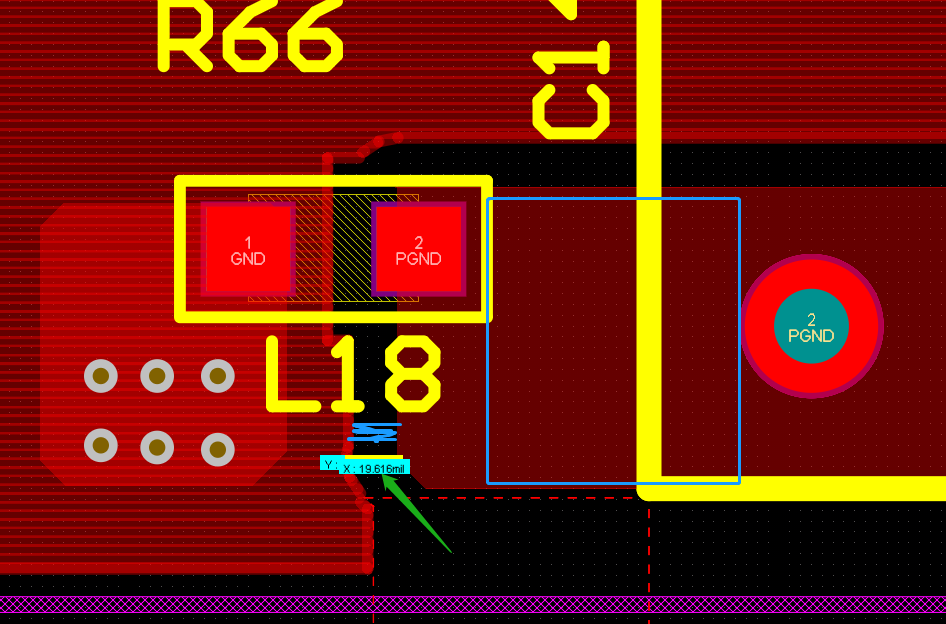

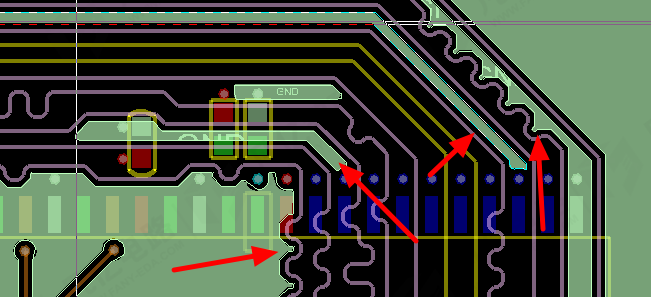

跨接器件旁边要多打地过孔,间距最少1.5mm,建议满足2mm,有器件的地方可以不满足2.网口差分需要进行对内等长,误差5mil3.模拟信号走线需要加粗,建议10-12mil4.反馈信号需要从电容后面取样,走10mil即可5.数据线之间等长需

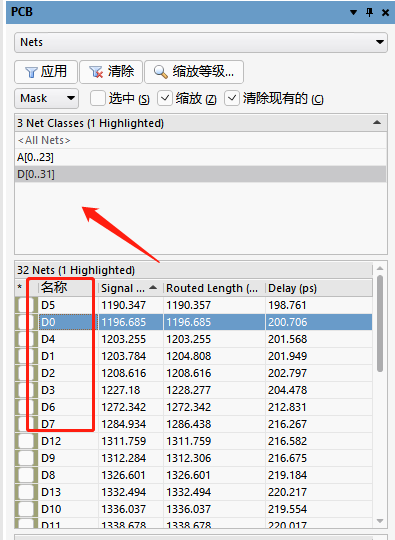

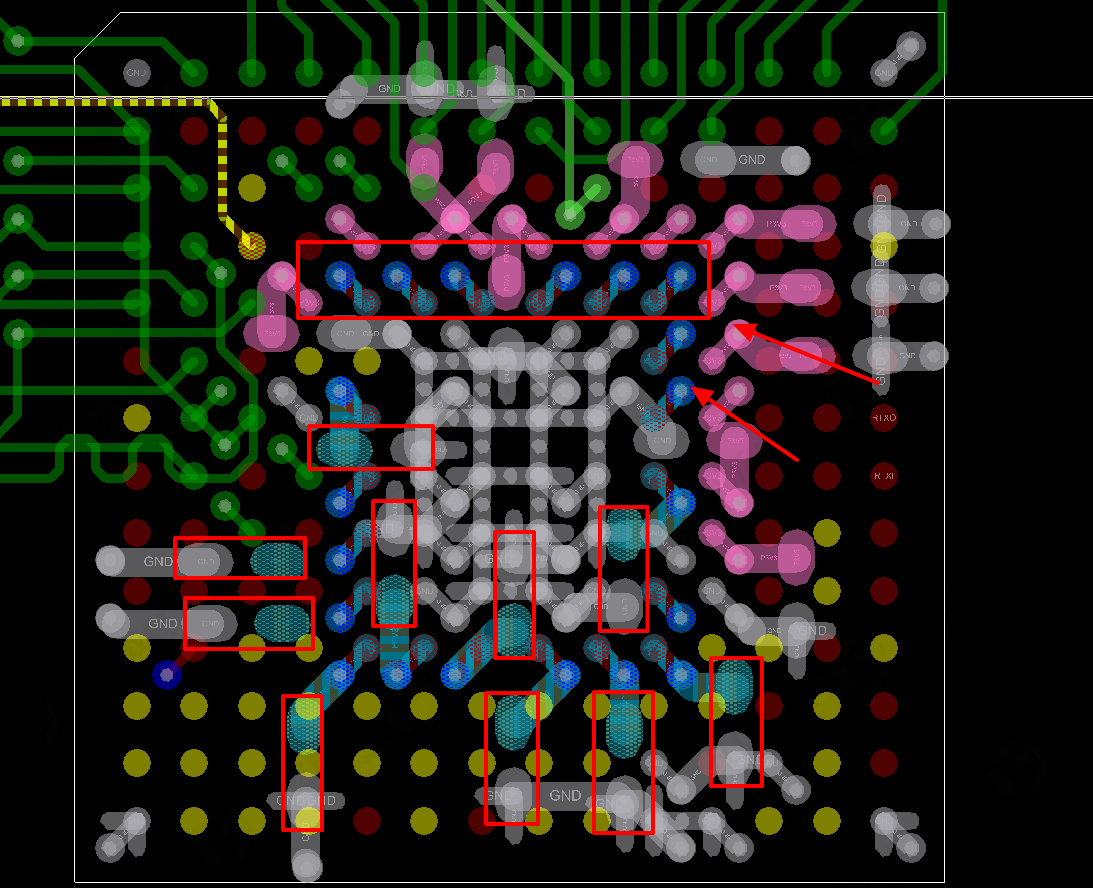

数据线高八位和低八位要分别进行分组等长,一组9根2.地址线等长不符合原理图要求3.等长注意一下不要有直角4.地址线分组需要把时钟信号,读写,控制都添加进来以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访

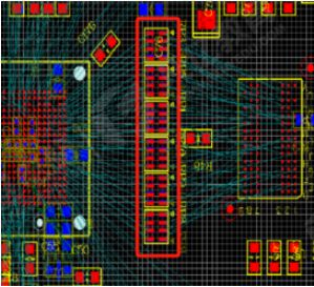

在DDR的设计中,需要对数据线及地址线进行分组及等长来满足时序匹配,通常DDR的数据线之间的长度误差需要保证在50mil以内,地址线的长度误差需要保证在100mil以内。执行菜单命令【设计】-【规则】或者使用快捷键DR打开规则约束器,在“H

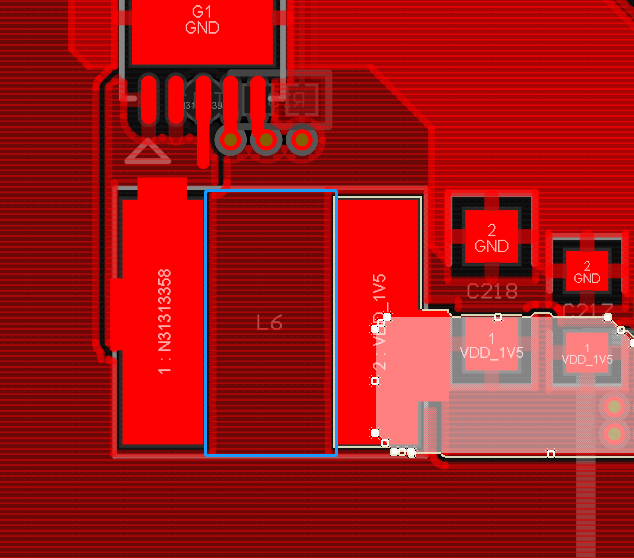

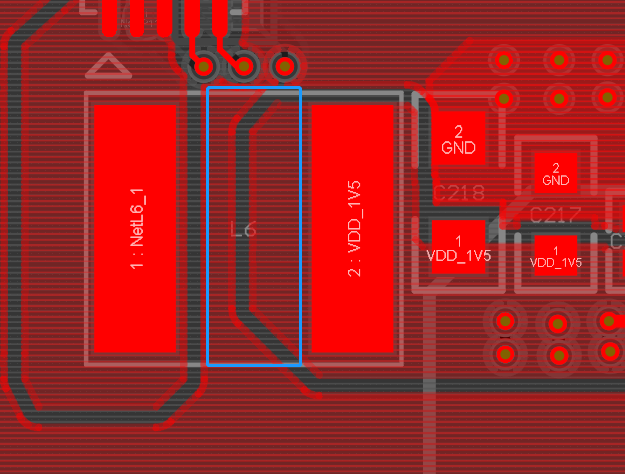

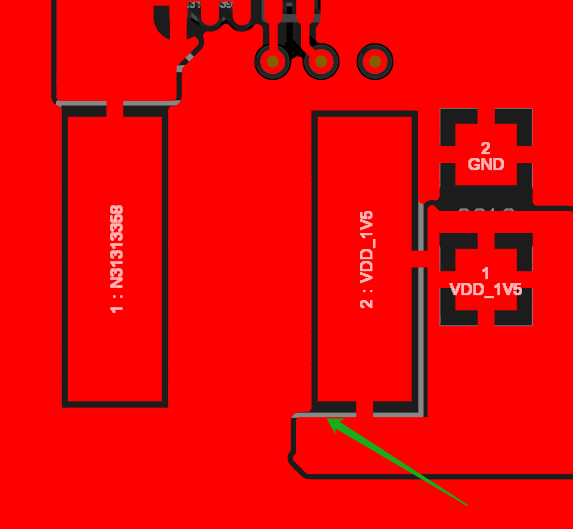

电感所在层的呢恩不需要挖空2.差分线对内等长处理不当,锯齿状等长,凸起高度不得超过线距的两倍3.注意数据线等长需要满足3W规则4.差分出线要尽量耦合5.存在多余的线头6.注意过孔不要上焊盘7.注意器件摆放过近,建议最少1.5mm8.过孔需要

电感所在层内部需要挖空处理2.滤波电容摆放应该先大后小3.差分线处理不当,锯齿状等长,凸起高度不得超过线距的两倍4.数据线等长需要满足3W规则5.地址线也要满足3W规则6.此处不满足载流,VREF电源最少需要加粗到15mil7.此处走线需要

存在多处尖岬铜皮和孤岛铜。2. 多处器件摆放干涉,如生产会造成两个器件重叠无法焊接。3.部分管脚存在开路。4.数据线分组错误,少了LDQM和HDQM5.地址线分组错误,缺少部分信号;以设计规范为准。以上评审报告来源于凡亿教育90天高速PCB

1.芯片下方电容要均匀分布。2.数据线等长组分组错误,两组线分别缺少LDOM、HDQM。3.数据线等长错误,应该控制误差50mil4.地址线等长分组错误,缺少部分网络5.电源输入线宽不一致,电容输入输出都需要加宽。6.多存在多处尖岬铜皮。7

DDR3 2片:电感内部挖空处理。注意电源铺铜不要出现这种瓶颈处:等长线注意要保证3W间距,去调整出来:数据线需要满足等长误差,还存在报错:数据线也要满足3W间距自己注意走线跟过孔的间距规则:分割带尽量大于20MIL:以上评审报告来源于凡亿

线宽不一致,导致阻抗不连续走线需要保持3w间距规则地址线分组错误,缺少信号时钟线等长错误电源走线多处没有加粗数据线等长误差控制100mil范围内以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫

一般我们在进行PCB设计时可能会留意到有些信号会串联一个电阻,那么大家是否有想过所串联的电阻是有什么作用呢?大家可以看一下下面图示的案例,信号是从CPU处出来再接到DDR颗粒的,每一个DDR数据线都有串联一个电阻,其实这个串联电阻的作用是进

扫码关注

扫码关注