- 全部

- 默认排序

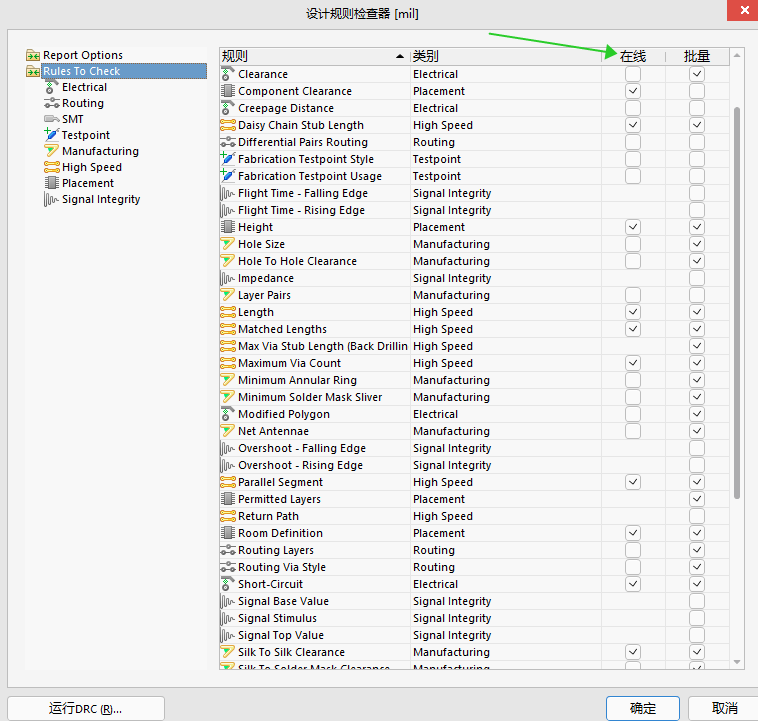

我们在进行PCB设计的时候,最后我们需要去进行DRC的检查,检查完成之后会出现各种总各样的报错,当然其中常见的间距报错,规则报错我们都知道怎么更改,也能看懂大概的意思。可以有时候碰到一些比较少见的报错,就会不知道这个报错的原因是什么 了。

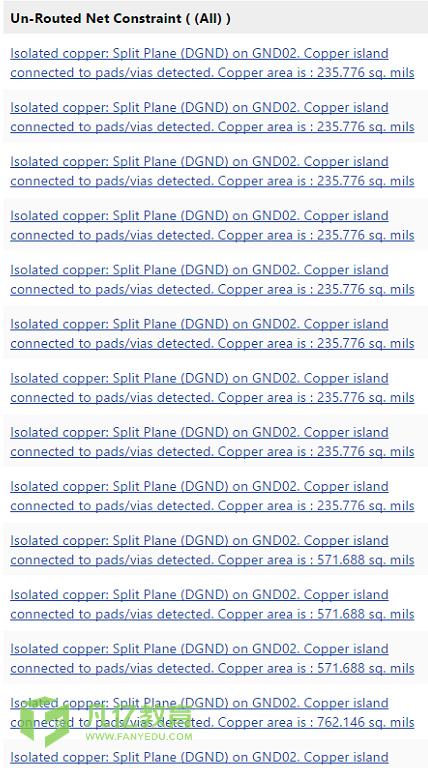

我们在进行PCB设计的时候,最后我们需要去进行DRC的检查,检查完成之后会出现各种总各样的报错,当然其中常见的间距报错,规则报错我们都知道怎么更改,也能看懂大概的意思。可以有时候碰到一些比较少见的报错,就会不知道这个报错的原因是什么 了。比如今天要讲解的DRC报错中的“Isolated copper:Split pllane....”的报错,为了方便大家了解这项报错,我们找到了素材图片如下:

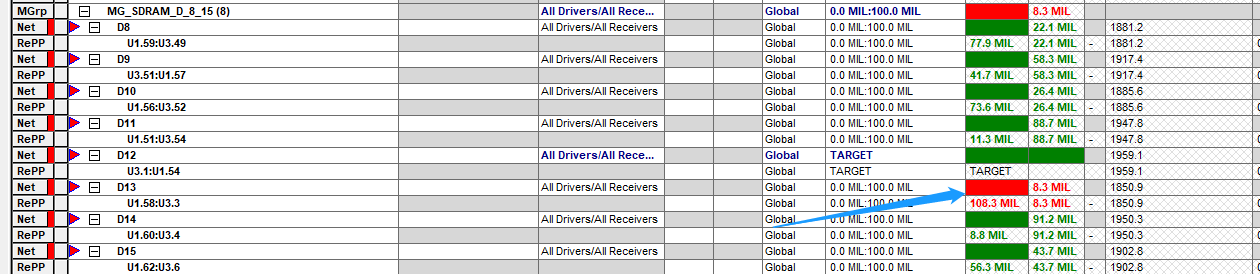

1SDRAM注意数据线等长存在报错2DDR注意差分出线呀尽量耦合2.差分线对内等长处理不当,锯齿状等长不能超过线距的两倍3.差分要设置对内等长误差5mil4.滤波电容尽量保证一个管脚一个,靠近管脚摆放5.注意电源管脚扇孔走线需要加粗以上评审

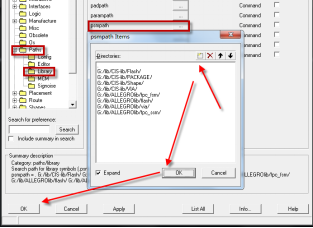

答:在将网表导入到PCB的过程中,常会由于带通孔的PCB封装内的焊盘中Flash在相应的路径中找不到,而导致导网表报错,报错内容及提示如图4-93所示: 图4-93 错误提示示意图根据图4-93所示,我们可以分析得出以下几个结论:Ø 导网表时报错的器封装名是CON2X5_2P54M。Ø PCB封装中焊盘名为PAD100SQR165THR的焊盘不能被完整提取到,原因是在设置的库路径下找不到名为THR100X165C150X180X040的Flash。对于此

扫码关注

扫码关注