- 全部

- 默认排序

在线DRC如何打开

如题:在线DRC如何打开2018-11-20 10:07 上传已经设置了在线DRC,但是不会实时报错,显示绿色,在手动运行规则检查后冲突的地方会变绿,修改后,还是绿色,只有再次手动运行规则检查后绿色才会消失。请问这是哪里设置有问题?

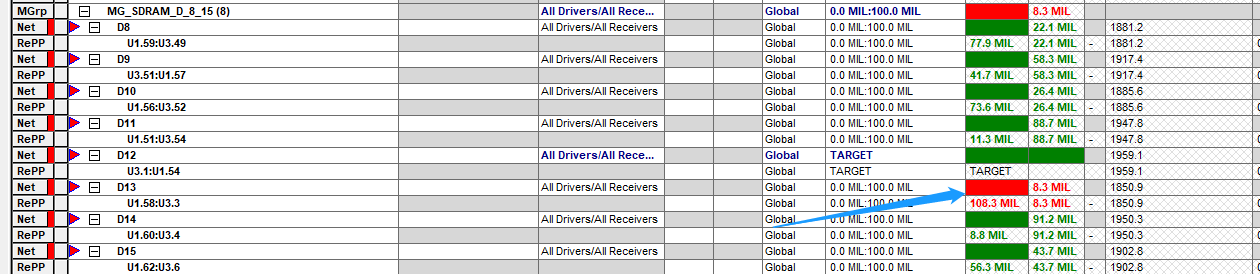

1SDRAM注意数据线等长存在报错2DDR注意差分出线呀尽量耦合2.差分线对内等长处理不当,锯齿状等长不能超过线距的两倍3.差分要设置对内等长误差5mil4.滤波电容尽量保证一个管脚一个,靠近管脚摆放5.注意电源管脚扇孔走线需要加粗以上评审

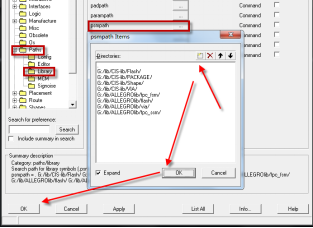

答:在将网表导入到PCB的过程中,常会由于带通孔的PCB封装内的焊盘中Flash在相应的路径中找不到,而导致导网表报错,报错内容及提示如图4-93所示: 图4-93 错误提示示意图根据图4-93所示,我们可以分析得出以下几个结论:Ø 导网表时报错的器封装名是CON2X5_2P54M。Ø PCB封装中焊盘名为PAD100SQR165THR的焊盘不能被完整提取到,原因是在设置的库路径下找不到名为THR100X165C150X180X040的Flash。对于此

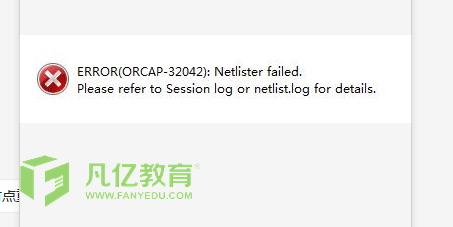

我们在进行原理图设计的时候,完成之后就需要去进行网表的导出,然后在pcb中去进行设计。有很多学员在原理图导出网表的这一操作中会出现各种各样的报错,那么今天我们就来看看最常见的一项导出网表的报错的解决办法,即”Netlister failed”的报错。

本视频采用Altium designer 19,分享关于软件的系统规则的导入操作演示和导出系统规则的操作演示注意事项,同时关于PCB界面的规则的导入操作和导出的操作的演示,以及注意事项和操作的演示。

老师您好!我在给PCB增加内电层负片地的时候,存在死铜、岛铜无法去除的问题,在AD19上可以通过增加FILL消除DRC报错,在AD20里面这个方法无效,反复试验多次,最后只能缩小铺铜间距或者挪过孔的方法才可以消除;请问AD20里面有没有办法杜绝死铜产生?铺铜的时候可以勾选去死铜,但是负片里面没的选啊

扫码关注

扫码关注