- 全部

- 默认排序

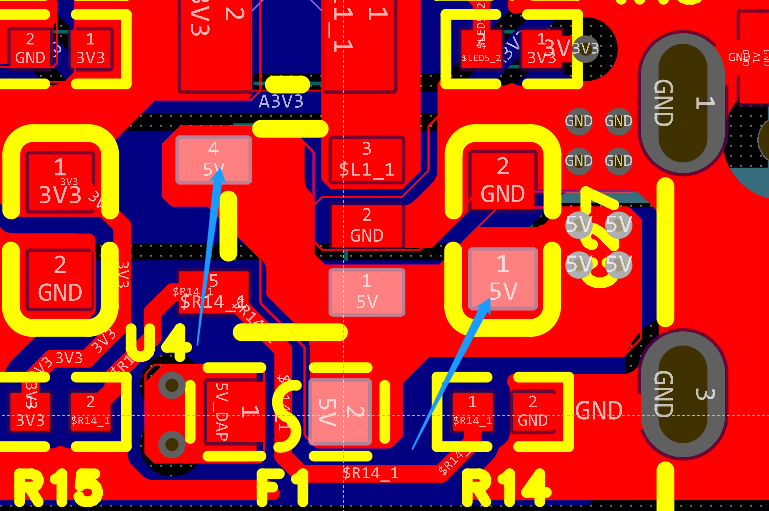

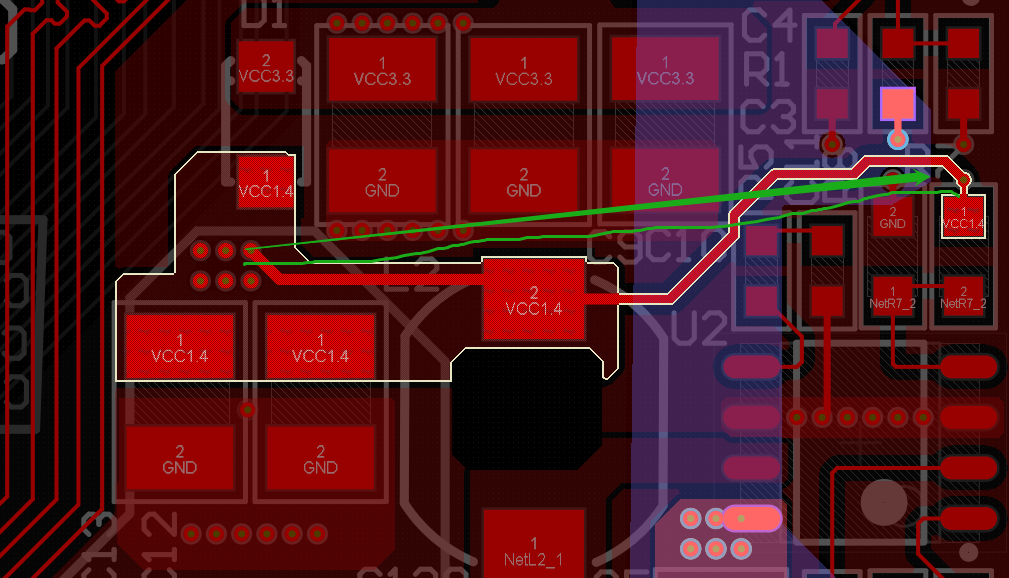

1.电源输入的滤波电容应该靠近输入管脚(4脚)放置2.走线尽量不要从器件中间穿过3.差分线处理不当,锯齿状等长,凸起高度不得超过线距的两倍4.时钟信号包地需要在地线上间隔150mil-200mil添加一个地过孔

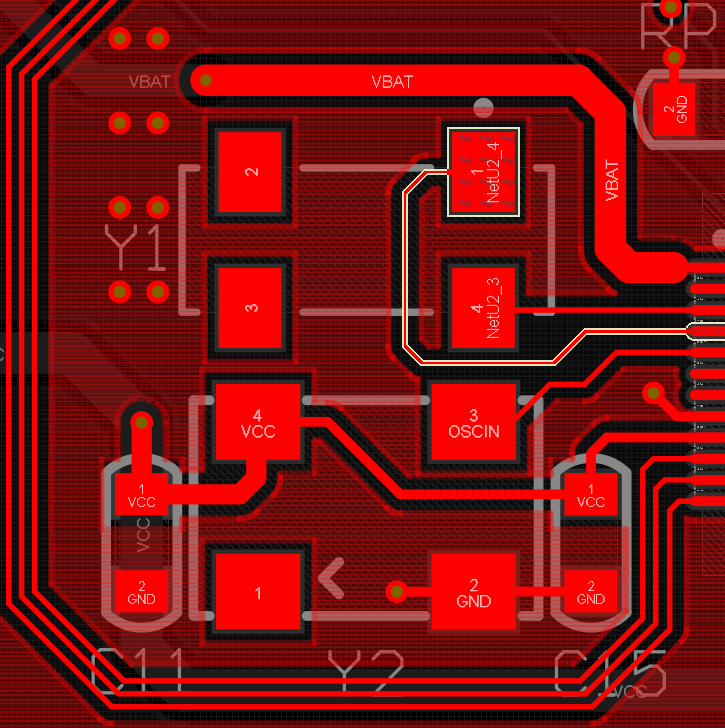

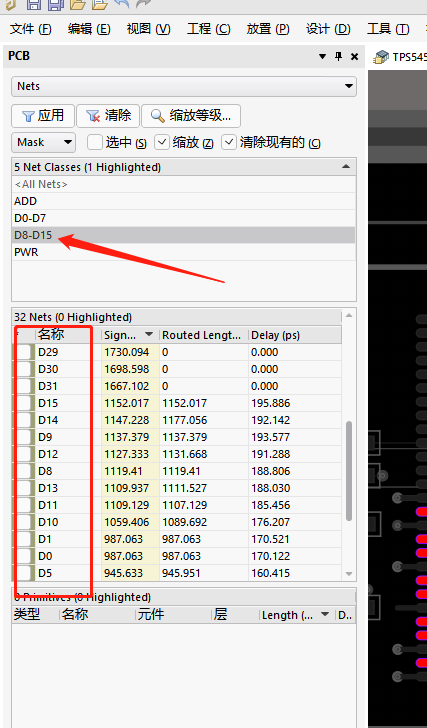

晶振需要包地,并且打上地过孔2.确认一下此处是否满足载流,自己加粗线宽3.差分包地需要在地线上打上地过孔4.差分线处理不当,锯齿状等长,凸起高度不得超过线距的两倍5.RS232尽量不要同层布线,如需同层建议间隔5W以上,不要走差分以上评审报

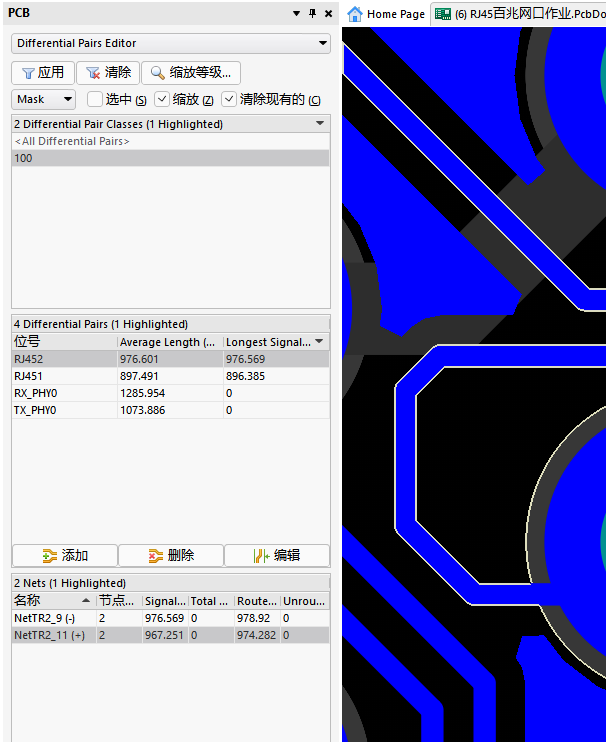

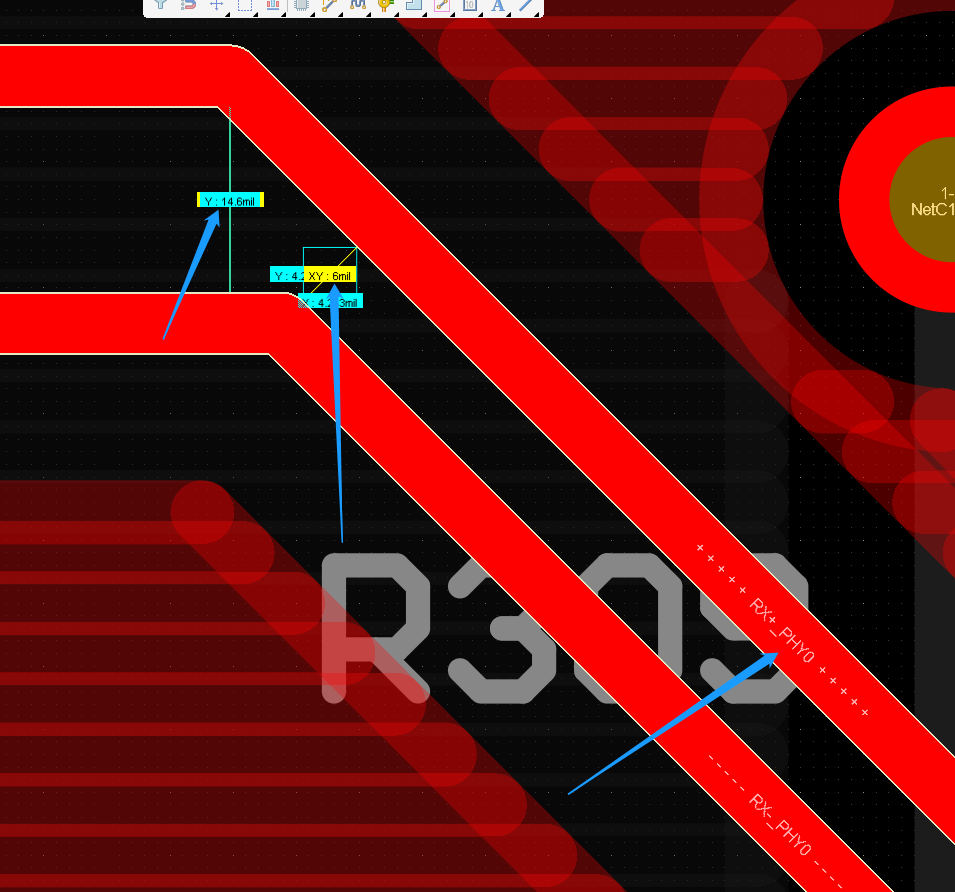

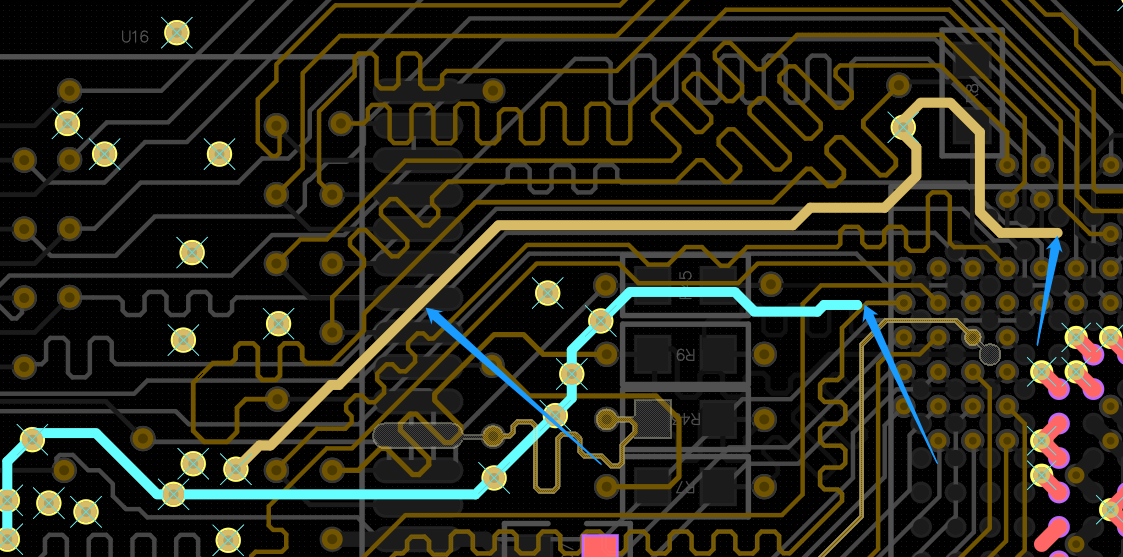

差分对内等长误差5mil2.未添加TR和RX的class3.包地要在地线上 打过孔4.器件干涉5.差分出线要尽量耦合6.时钟信号需要包地处理,并且打上地过孔7.pcb上存在两处开路以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需

PCB板的布线设计过程是一个复杂而又简单的过程,要想很好掌握布线,电子工程师需要经过多次项目设计多次试验学习积累经验,而EDA工具的自动布线功能只能帮工程师缩短一些时间,工程师需要刻苦学习巩固基础,所以今天我们阿里学习如何为电源和地线做好布

差分走线不满足间距2.差分出线要尽量耦合,走线不要有直角差分走线都存在问题,自己后期重新优化一下3.网口差分要进行对内等长,误差5mil5.pcb上存在开路6.线宽尽量保持一致7.时钟信号包地可以在地线上多打地过孔8.确认此处是否满足载流9

反馈要从电容后面取样2.注意过孔不要上焊盘3.走线尽量不要从电阻电容中间穿4.丝印调整不到位,注意丝印不要上焊盘5.顶层BGA里面的铜尽量挖掉6.此处走5mil地线太细,建议最少12mil以上以上评审报告来源于凡亿教育90天高速PCB特训班

器件布局应该在BGA上对应焊盘的方向,尽量缩短走线,2.差分对内等长Space的高度是1倍到2倍间距的高度。3.差分包地应该尽量包过来4.走线在焊盘中应该和焊盘保存等宽5.包地线很长一段走线没有打孔。以上评审报告来源于凡亿教育90天高速PC

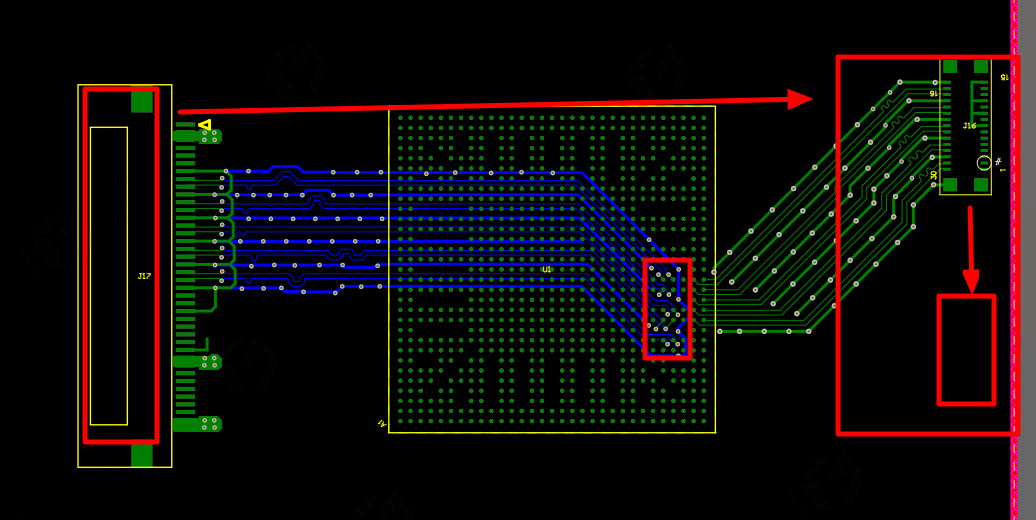

添加的地线尽量多打地过孔2.数据线一组尽量走一起,中间不要有地址线3.此处网络需要加入class一起进行等长4.电源需要处理一下,器件摆放尽量中心对齐以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问

电流检测电路设计方案(一)低端检流电路的检流电阻串联到地(图1),而高端检流电路的检流电阻是串联到高电压端(图2)。两种方法各有特点:低端检流方式在地线回路中增加了额外的线绕电阻,高端检流方式则要处理较大的共模信号。图1 所示的低端检流运放

数据线一组只有9根线,其他信号不要添加进来,高八位少一根LDQM12.数据线和地址线建议添加一根最少20mil的地线进行隔开3.过孔里存在多余的线头4.地址线分组错误,有电阻几根网络也需要添加进来进行一起等长,还有时钟信号5.走线需要从焊盘

扫码关注

扫码关注