- 全部

- 默认排序

一、STM8S105S4T6CIC MCU 8BIT 16KB FLASH 44LQFPSTM8S105S4T6C Access line 8位微控制器提供16KB 闪存程序存储器,以及集成的真数据EEPROM。STM8S105x4/6 A

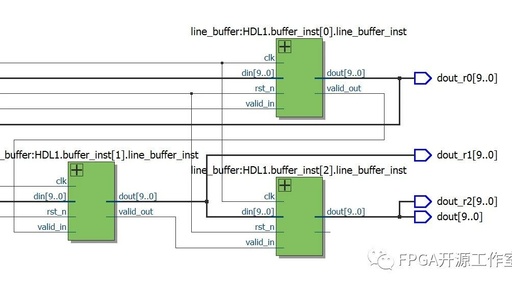

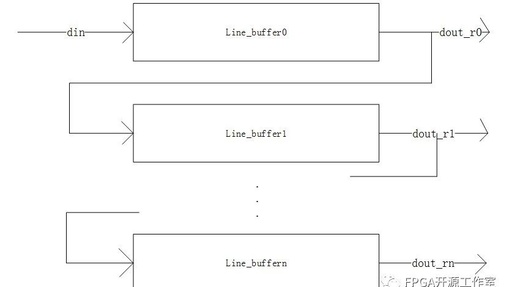

FPGA图像处理之行缓存(linebuffer)的设计二作者:OpenS_Lee01背景知识 在FPGA数字图像处理中,行缓存的使用非常频繁,例如我们需要图像矩阵操作的时候就需要进行缓存,例如图像的均值滤波,中值滤波,高斯滤波以及sobel边缘查找等都需要行缓存设计。这里的重要性就不在赘述。0

FPGA图像处理之行缓存(linebuffer)的设计一背景知识 在FPGA数字图像处理中,行缓存的使用非常频繁,例如我们需要图像矩阵操作的时候就需要进行缓存,例如图像的均值滤波,中值滤波,高斯滤波以及sobel边缘查找等都需要行缓存设计。这里的重要性就不在赘述。FPGA实现图1 行缓存菊花链

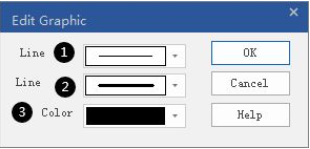

设计当中,可以通过放置辅助线来标识信号方向或者对功能模块进行分块标识。1)执行菜单命令“Place-line”(快捷键“Shift+L”),激活放置状态。2)在一个合适的位置单击鼠标左键,找到下一个位置单击鼠标左键确认结束点。3)在放置之后

高通晶振设计指导

前言:1、随着目前PCB越来越小,越来越薄,导致更加严重的散热问题2、XTAL_IN/XTAL_OUT和GND_line可以作为热源的传热路径,导致GPS/GNSS受到影响。3、布局区域约束要求晶振布局必须靠近PMIC 一、布局要求1、晶振需要远离PMIC,需要保证XTAL_IN/OUT的距离在3~

双列直插封装(dual in-line package)也称为DIP封装或DIP包装,简称为DIP或DIL,是一种集成电路的封装方式。DIP插件工艺是在SMT贴片工艺之后,是PCBA工艺中的一部分,DIP插件是指不能被机器贴装的大尺寸元器件

PADS软件封装库内包含4个内容:Logic Decal(逻辑库)、PCB Decal(封装库)、line(线库)、Part(元件库),设计师进行原理图设计前,必须先制作好元件库。ØLogic Decal(逻辑库):表示元件的逻辑功能。ØP

前文我们已用Clip API来实现Java播放本草纲目,接下来将用 SourceDataline来实现Java播放本草纲目,希望对小伙伴们有所帮助。2、SourceDatalineSourceDataline API是Java的一个缓冲或流

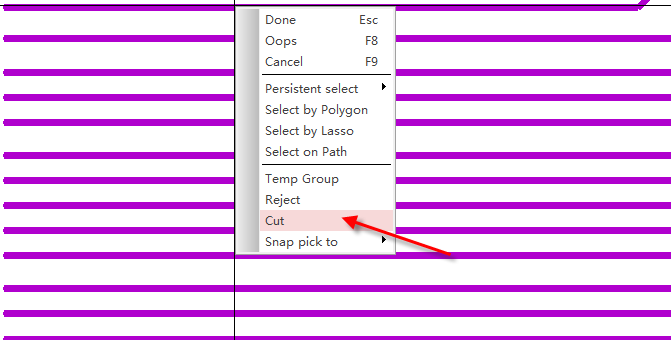

答:CUT功能,就是切除一整段线中间一部分的功能,是删除功能下所附属的一个功能,可以CUT的对象可以是电气走线,如cline,也可以说非电气走线,如line,操作的方法都是一致的。这里以CUT一段Cline为例,讲解一下CUT功能的使用

答:第一步,打开程序,选择File->new命令,在弹出的对话框中进行如下图设置,如图4-51所示; 图4-51 新建封装按系统模板示意图第二步,选择你需要新建的封装类型,如图4-52所示,具体参数的含义如下所示: 图4-52 选择封装模板示意图Ø DIP: Dual-In-line components/双列引脚元件。Ø SOIC: Small outline Integrated Circuits/小外形集成电路。Ø

扫码关注

扫码关注