- 全部

- 默认排序

新手有个问题想请教各位,allegro里面怎么连续旋转器件,就类似AD里面那种,每次旋转还要重新输入一下角度,感觉很费劲。/辣眼睛 度娘也没给到我合理的解释/辣眼睛

阿狸狗破解大师破解cadence spb17.4后,发现allegro lib creator 17.4,启动显示license not availabile,could not acquire application license 请问要怎么结局手动破解也试过解决请问要怎么解决呀?或者,这个组件

注意电感当前层的内部需要挖空处理:注意反馈信号走8-12MIL就可以了:其他的没什么问题,注意电感内部需要挖空,需要修改的。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:http

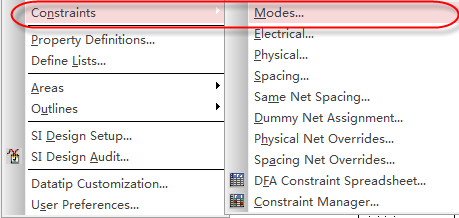

答:做PCB设计时,有些区域可以设置禁止铺铜,但是允许走线。第一步,点击Setup-Areas-Shape Keepout,在需要禁止铺铜的区域画好禁示区域,如图6-327所示;

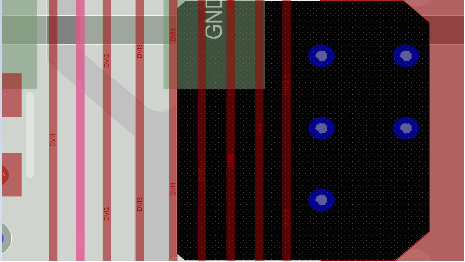

答:使用Allegro进行设计时,焊盘间飞线有2种显示方式,一种是焊盘到焊盘,一种是按最短距离显示,按最短距离显示,可在走线的时候让飞线指示到离另一连接点最近的位置。

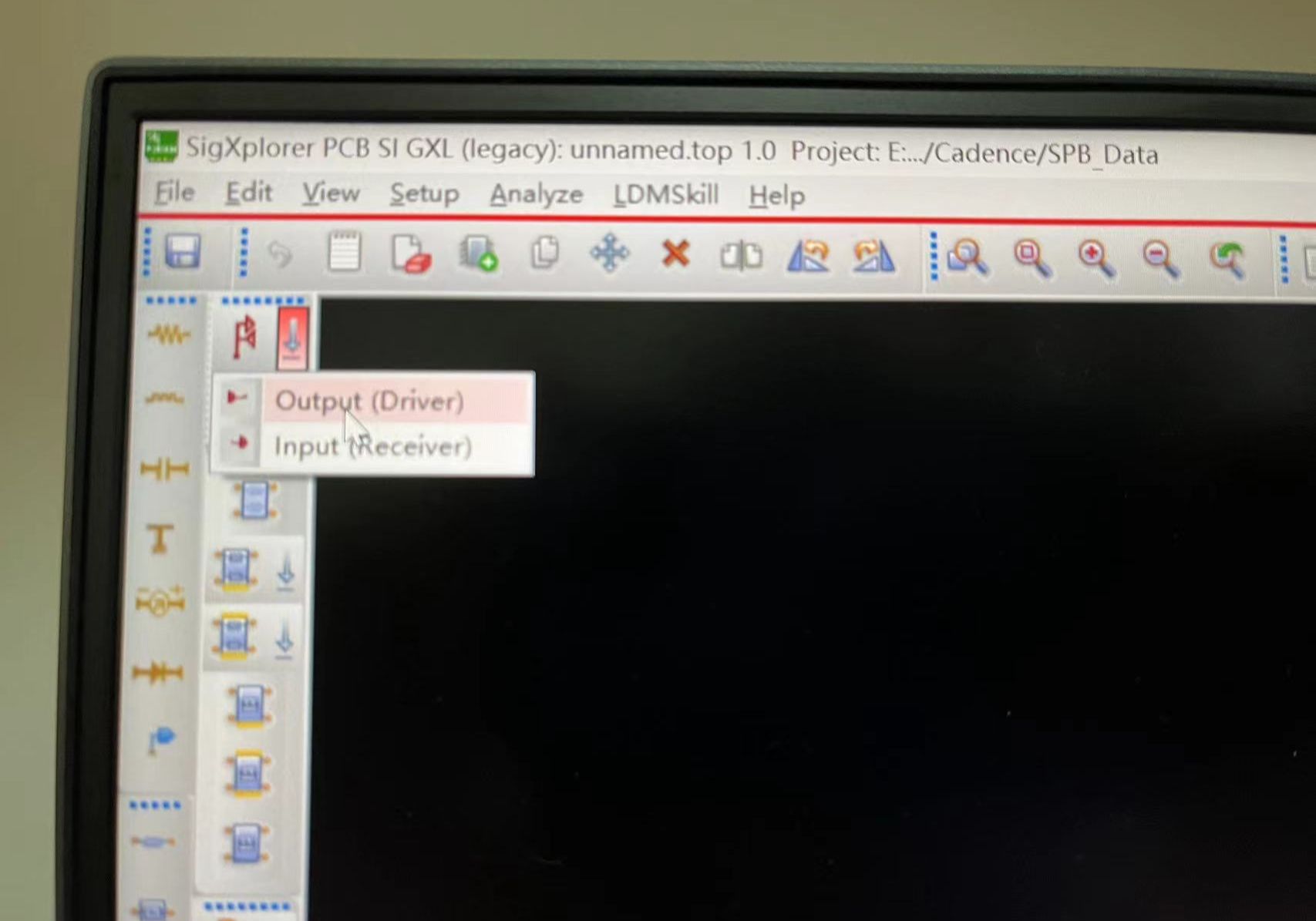

答:我们在时序等长时,除了考虑信号线的走线的长度以外,在高速设计领域里还需要考虑封装本身的引脚长度。所谓封装引脚长度,指的就是元器件封装内部的引脚长度,这个长度一般芯片的厂家会提供这数据,我们要做的就是将数据导入到规则管理器中,与等长一起处理,具体的操作步骤如下:

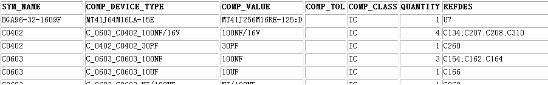

答:我们一般输出元器件清单,也就是BOM表单的都是从原理图进行输出,其实,从设计完成的PCB文件也是可以输出BOM清单的,具体的操作步骤如下所示:第一步,执行菜单命令Tools-Quick Reports,对PCB中的信息进行报告,我们在其下拉菜单中选择“Bill of Materrial Report(condensed)”,进行元器件信息的报告;

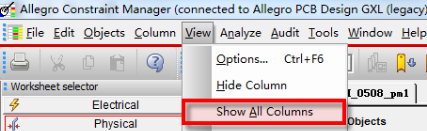

答:正常情况下CM规则管理器中属性较多,有很多列,如果有部分列我们不想显示,则可以隐藏,具体操作的步骤如下所示:第一步,点击Setup-Constraints-Constraint Manager选项,调出规则管理器。然后找到想隐藏的属性列(如Max Length),然后右击点击Hide Column选项,如图5-196所示,即可隐藏此列内容;

扫码关注

扫码关注