- 全部

- 默认排序

存在多处开路地网络后期自己在bottom层铺铜进行连接2.采用单点接地,此处可以不用打孔,只需要在芯片中心打孔进行回流即可3.输入打孔要打在滤波电容的前面4.输出打孔要打在滤波电容后面5.以上评审报告来源于凡亿教育90天高速pcb特训班作业

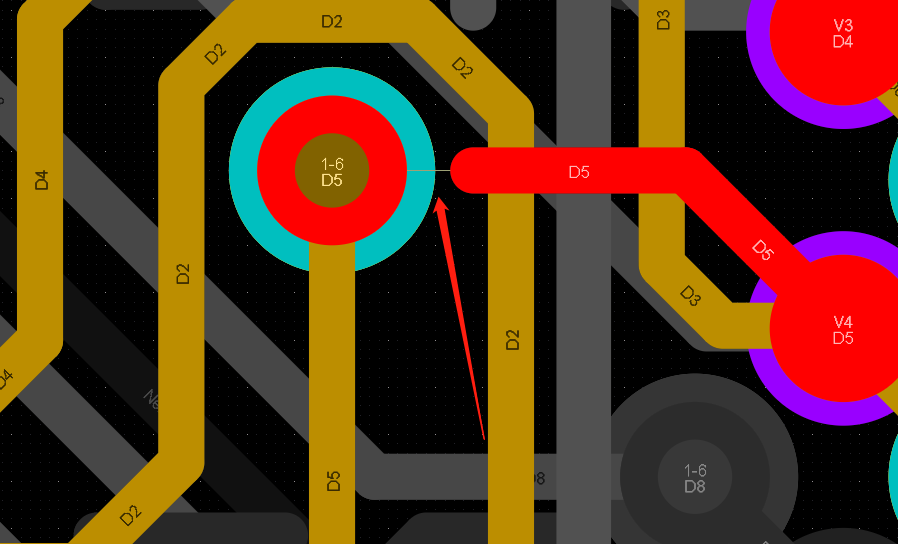

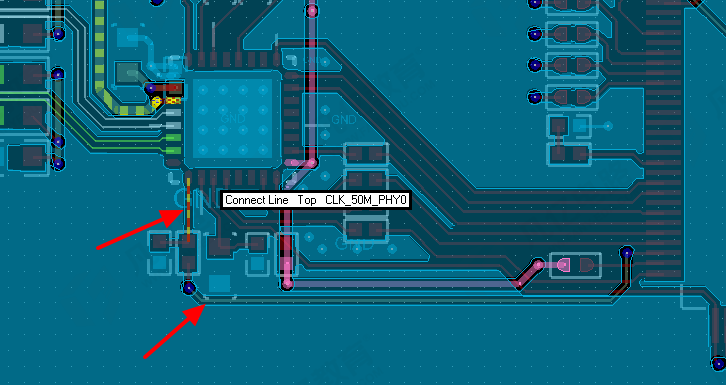

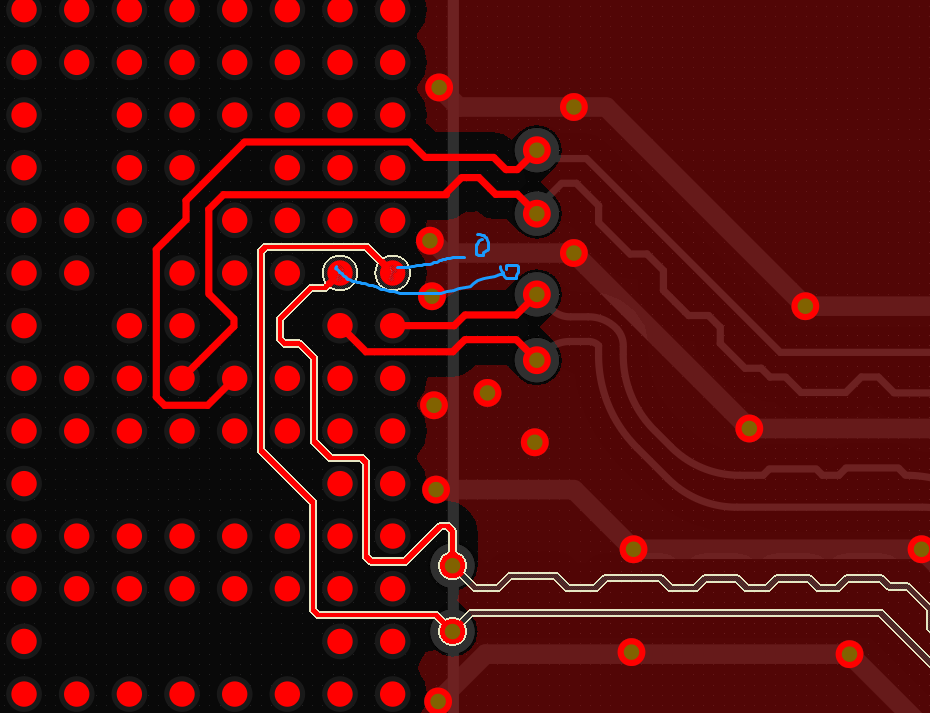

存在开路报错2.过孔尽量不要打在电阻中间3.走线尽量不要有直角,建议钝角4.时钟信号等长不符合规范5.地址线等长存在报错,以上评审报告来源于凡亿教育90天高速pcb特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https

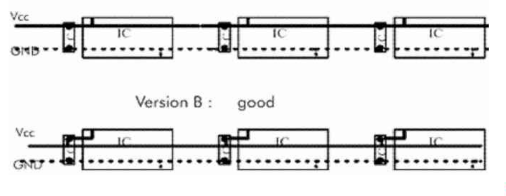

电源和地是高速pcb设计中的重要对象,它们的布局布线处理好坏直接决定着成品的性能运行和串扰大小,若是稍有不慎,很容易拖慢项目进度。所以下面讲讲电源和地的高速pcb布线处理方法,希望对小伙伴们有所帮助。第一,尽量给出单独的电源层和地层;即使要

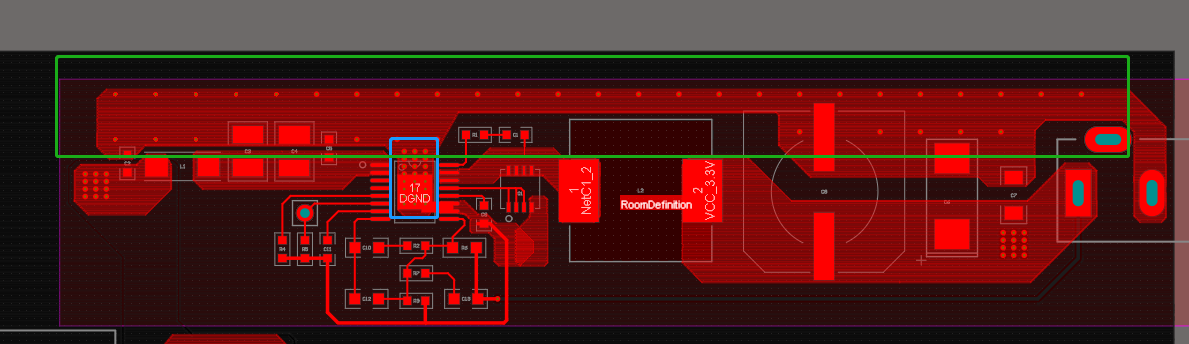

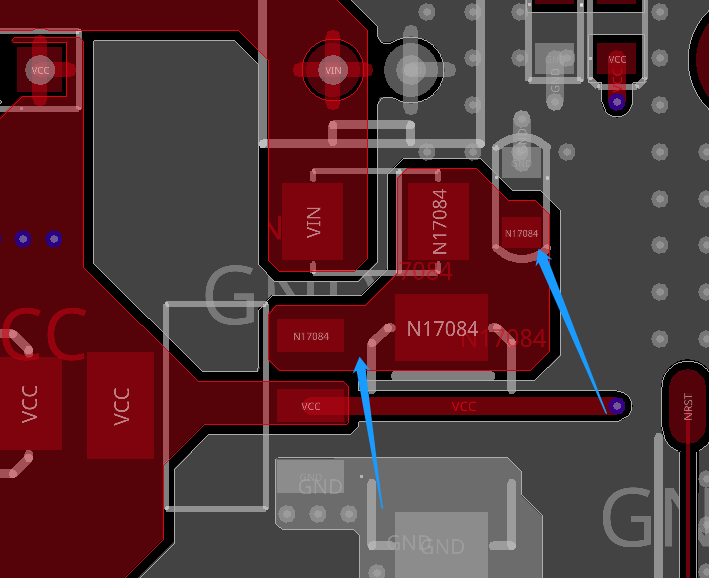

采用单点接地只需打孔在散热焊盘上,其他地方不用打孔,散热过孔需要开窗处理2.电感所在层的内部需要挖空处理3.其他没什么问题以上评审报告来源于凡亿教育90天高速pcb特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https

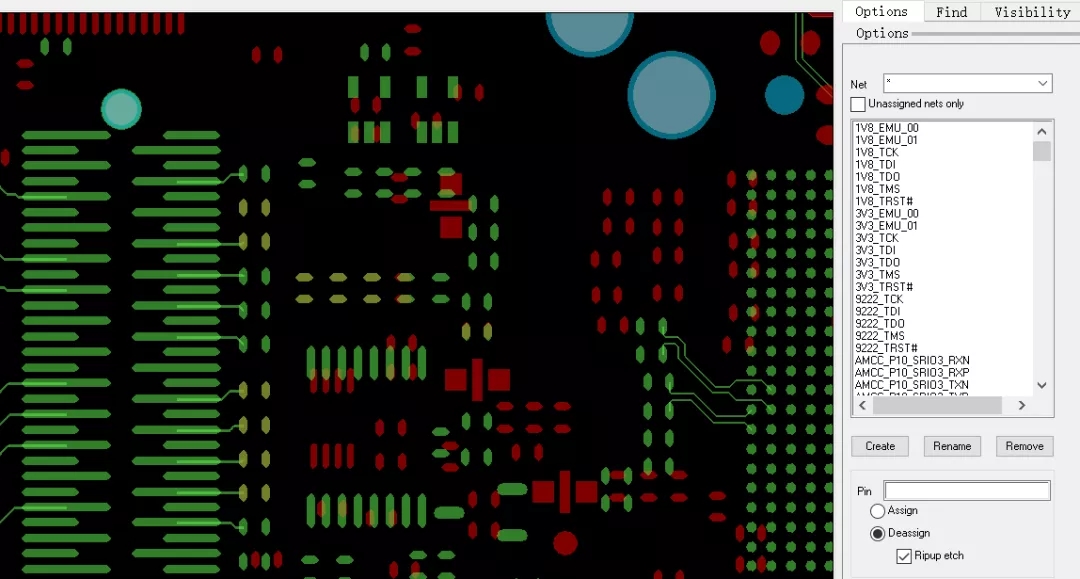

Allegro的全称是Cadence Allegro PCB Designer,是Cadence公司推出的一个完整的、高性能印制电路板设计套件。通过顶尖的技术,它为创建和编辑复杂、多层、高速、高密度的印制电路板设计提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段定义、管理和验证关键的高速信号,并能抓住今天最具挑战性的设计问题。Allegro印制电路板设计提高了PCB设计效率和缩短设计周期,让您的产品尽快进入量产(目前高速pcb设计用的最多工具,就是Allegro)。

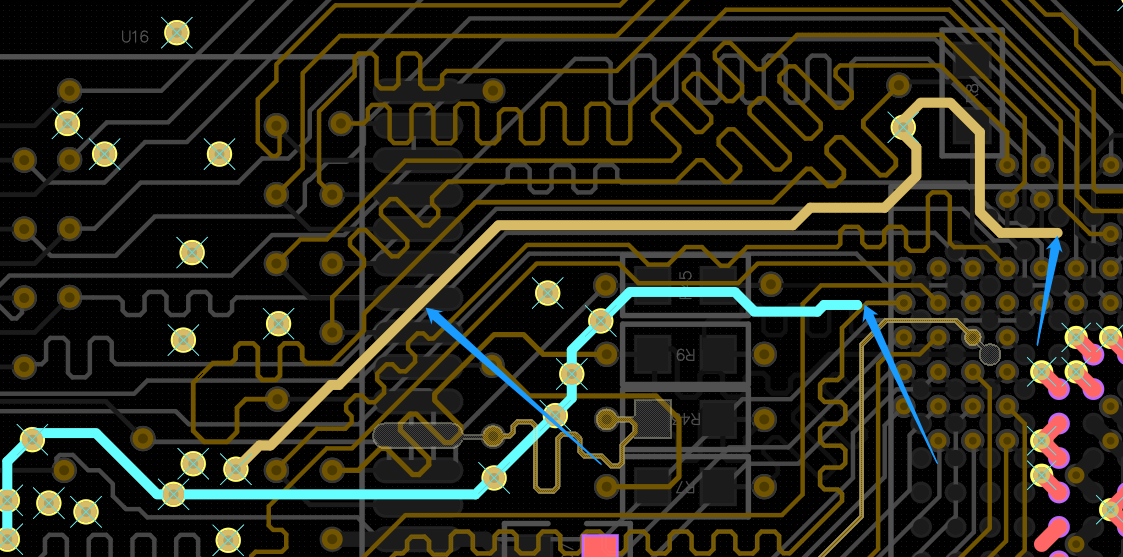

时钟走线包地打孔处理差分对内等长错误,按照规范绕线变压器下方铺铜挖空多处尖细铜皮rx、tx需要分别建立等长组,控制100mil误差等长以上评审报告来源于凡亿教育90天高速pcb特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教

电容按照先大后小摆放2.电源从最后一个电容后面进行输出3.差分信号包地,尽量在地线上打上过孔4.滤波电容靠近管脚均匀摆放5.晶振包地要包全注意过孔不要上焊盘以上评审报告来源于凡亿教育90天高速pcb特训班作业评审如需了解PCB特训班课程可以

添加的地线尽量多打地过孔2.数据线一组尽量走一起,中间不要有地址线3.此处网络需要加入class一起进行等长4.电源需要处理一下,器件摆放尽量中心对齐以上评审报告来源于凡亿教育90天高速pcb特训班作业评审如需了解PCB特训班课程可以访问

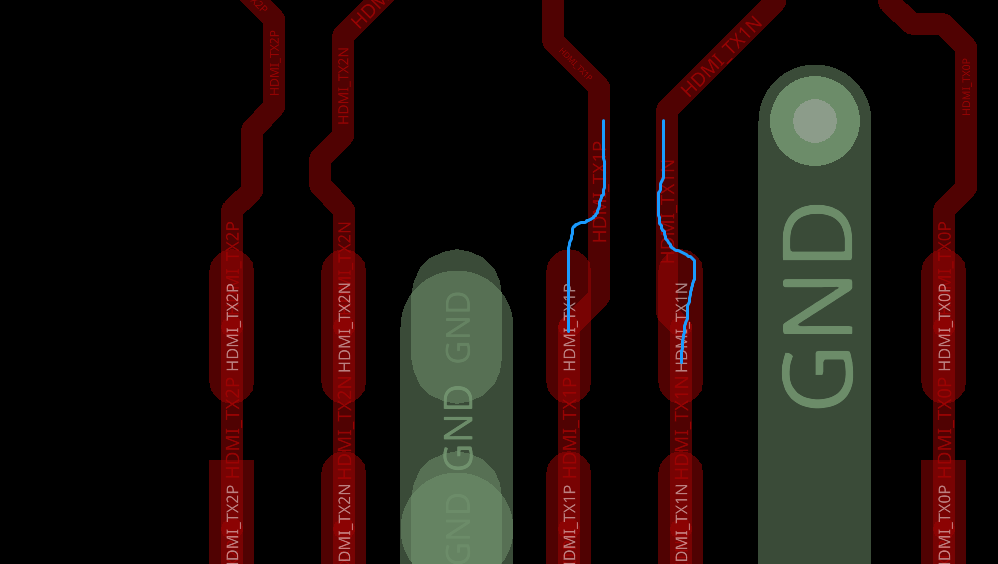

注意焊盘出线规范2.差分对内等长凸起高度不能超过线距的两倍,注意上面要满足3W3.差分包地需要再地线上打上地过孔,间距50-100mil4.差分对内等长存在误差报错5.注意地网络需要就近打孔以上评审报告来源于凡亿教育90天高速pcb特训班作

差分走线不满足差分规则,出线不耦合2.此处直接扇孔去底层连接3.差分线修理不当4.此处一个地不用进行处理,直接铺铜即可此处走线需要优化一下以上评审报告来源于凡亿教育90天高速pcb特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系

扫码关注

扫码关注