- 全部

- 默认排序

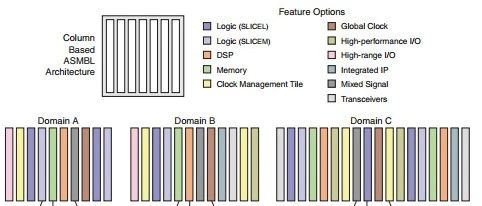

CLB是指可编程逻辑功能块(Configurable Logic Blocks),顾名思义就是可编程的数字逻辑电路。CLB是FPGA内的三个基本逻辑单元。CLB的实际数量和特性会依器件的不同而不同,但是每个CLB都可配置,在Xilinx公司的FPGA器件中,CLB由2个 相

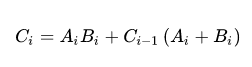

众所周知,信号电路主要分为模拟电路和数字电路,模拟电路主要负责模拟仿真传输等,数字电路负责电子电路的逻辑运算,很多小白基本上看不懂数字电路的逻辑电路,今天我们将分享举例,如何用译码器实现全加器,进一步了解逻辑电路。译码器(decoder)是

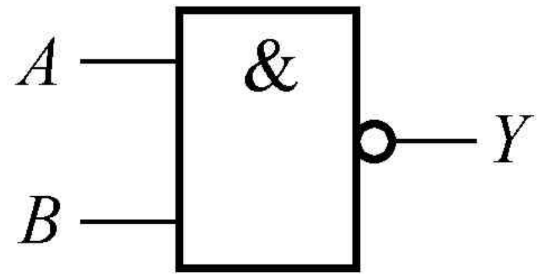

逻辑运算是学习数字电路的基础知识,按其结构可分为基础逻辑运算和复合逻辑运算,很多小白更了解前者,也就是基础逻辑运算,里面包括与(AND)、或(OR)、非(XOR),但很多人都不怎么熟悉复合逻辑运算,所以本文将详谈数字电路中的常见复合逻辑运算

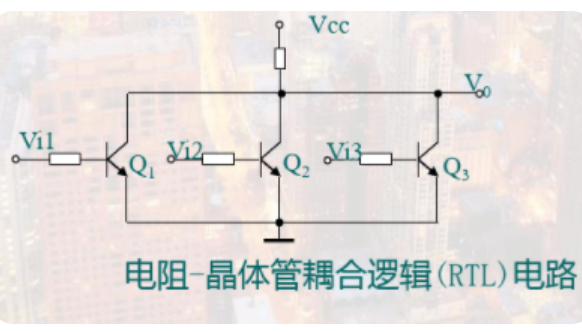

众所周知,晶体管具有检测、整流、放大、开关等多种特点,常用于电子电路中,也可以组成逻辑电路,在数字集成电路中应用广泛,但它同时也是许多小白初入数字电路的难题之一。今天将以小白最头疼的DTL、RTL、TTL三种晶体管逻辑电路为主,详谈其特点和

在数字IC系统设计时,触发器若是设计不当很容易出现,但很多小白都不知道触发器发生亚稳态后的输出情况,所以今天就讲讲,希望对小伙伴们有所帮助。一般来说,若数字系统只存在逻辑,那么工程师也就不会面临可靠性的问题,然而、实际上,所有逻辑电路处理的

对于FPGA工程师来说,RTL设计是常见的FPGA必不可少的设计环节,但对于小白来说,很多小白不懂RTL设计,甚至数次在FPGA或RTL设计常走歪路,所以本文将详谈RTL设计。1、使用Verilog进行RTL设计使用Verilog进行RTL

近日,科学组在一项概念验证研究中,成功创建能够执行简单逻辑功能的自组装蛋白质电路,该研究的成功表明:利用电子在量子尺度上的特性来创建稳定的数字电路是可行的。由于电路尺寸的减小,电路变得不可靠,这是因为创建电流所需的电子在量子尺度上表现得像波

组合逻辑电路设计,在任何特定时间只能在输入的时间取决于输出,电路的原始状态无关。“也就是说,组合逻辑电路输出电路的历史地位并不重要,电路不包括存储单元。组合逻辑表达方法有三种:真值表,逻辑表达式和电路原理图。在verilogHDL描述组合逻辑电路中,与真值表对应的是用户自定义原语;而与电路原理图相对应的是门级建模,有个绰号又叫结构化描述;与逻辑表达式相对应的则称为行为描述。

就生产而言,PCB工程师设计PCB板时,需要站在PCB板制造的角度,考虑制造的制程参数,从而提高制板直通率,降低过程沟通成本。比如说线宽、线距设计得是否足够,能否满足工厂的真实要求,孔到线、孔到孔之间的距离是否合规,这些要点在设计的时候都需要考虑清楚。而且在电子产品开发中,除了逻辑电路图设计,PCB

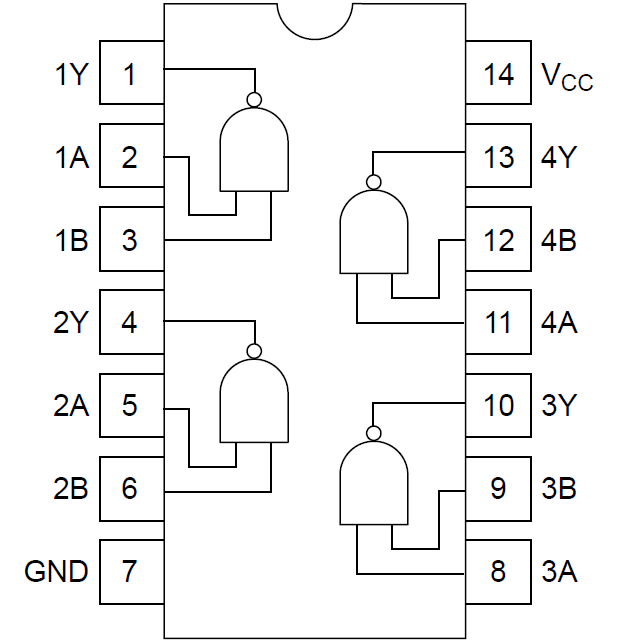

逻辑门电路是以简单的分立元器件组成而成,这里我们以一个简单的逻辑与非门电路74HC01为例讲解下创建方法,74HC01的逻辑电路图如图2-16所示,是由4个一样的逻辑与非门电路组合而成的。 图2-16 74HC01逻辑门示意图第一步,在olb文件单击鼠标右键,建立新的New Part,Name那一栏输入74HC01,PCB封装那一栏可以先不填写,下面的Parts per pkg输入4个,我们这个是由4个一样的与非门组成,所以做一个就可以了,然后Package Type选择Ho

扫码关注

扫码关注