- 全部

- 默认排序

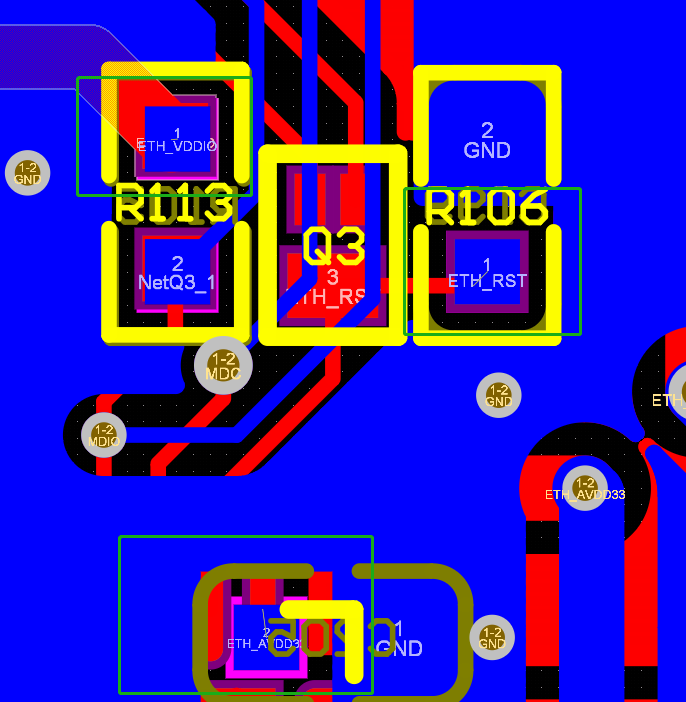

这里底层没有连接这里有不完全连接这里两个不同网络的地之间间距至少1.5mm以上这个时钟要包地处理以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taoba

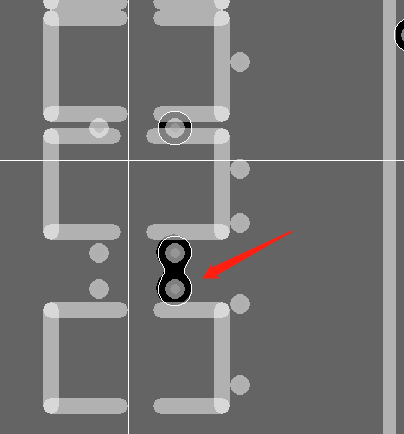

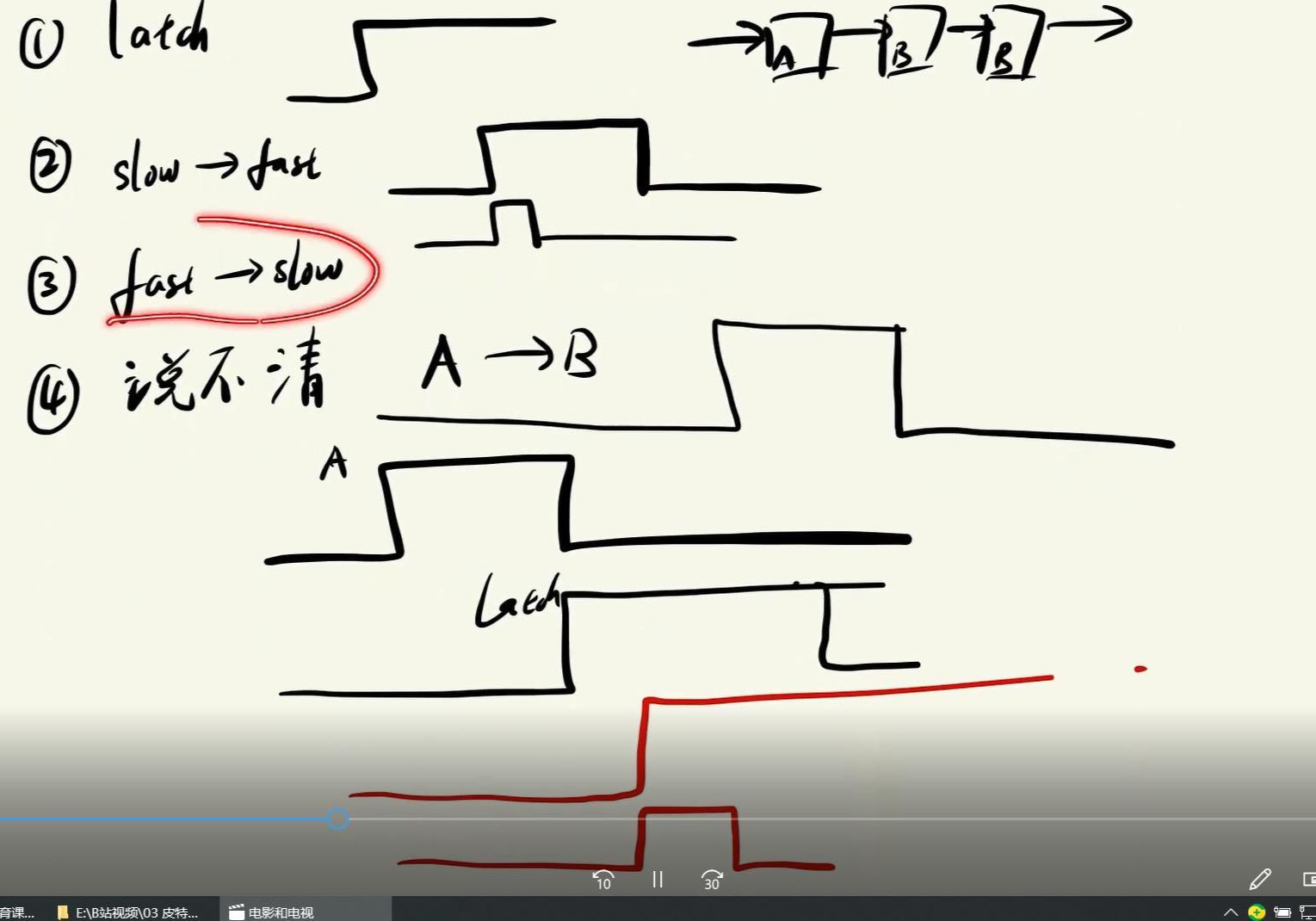

注意过孔间距,不要造成平面铜皮割裂:注意地址控制时钟组跟数据组可以用GND走线间隔开:下面的数据一致用GND走线隔开:其他的走线等长没什么问题了。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或

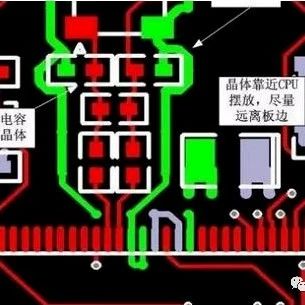

我们常把晶振比喻为数字电路的心脏,这是因为,数字电路的所有工作都离不开时钟信号,晶振直接控制着整个系统,若晶振不运作那么整个系统也就瘫痪了,所以晶振是决定了数字电路开始工作的先决条件。 我们常说的晶振,是石英晶体振荡器和石英晶体谐振器两种,他们都是利用石英晶体的压电效应制作而成。在石英晶体的两个电

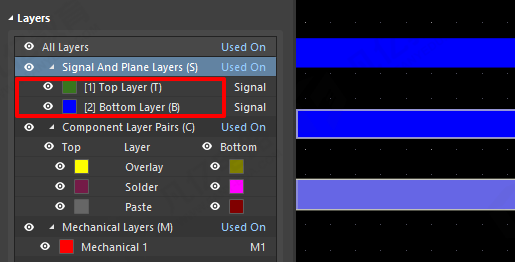

1.线宽要保持一致,线宽不一致会导致阻抗不连续。2.TF卡的时钟信号,与其他信号线的间距保证20mil左右,有空 间的情况下,包地处理。3.数据线等长错误,避免绕90度角等长。4.铺铜存在多处孤岛铜和尖岬铜皮以上评审报告来源于凡亿教育90天

答:PCB设计中常用的存储器有如下几种:Ø SDRAM,Synchronous Dynamic Random Access Memory(同步动态随机存储器)的简称,SDRAM采用3.3v工作电压,带宽64位,SDRAM将CPU与RAM通过一个相同的时钟锁在一起,使RAM和CPU能够共享一个时钟周期,以相同的速度同步工作,与 EDO内存相比速度能提高50%;

电子设计当中,经常用到差分走线,如USB的D+与D-差分信号,HDMI的数据差分与时钟差分等。虽然现在很多设计者都是在PCB中添加差分,但是还是有许多设计者习惯在PCB中就添加好差分。那么,如何在原理图中添加差分标识呢?

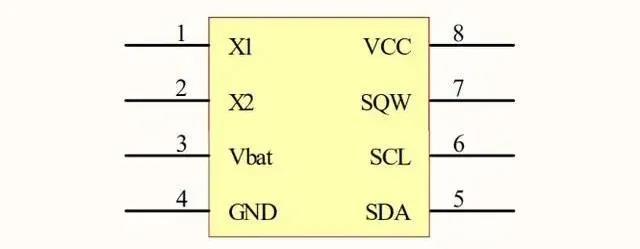

工程师在开发一个电路系统,往往会需要用到中央处理器,比如单片机、FPGA、或者DSP等等;当然一些简单的纯硬件电路项目方案例外,如充电器、热水壶等等。 作为单片机研发设计的项目,它的最小电路工作系统包含电源电路、复位电路、时钟频率电路;其中电源电路与复位电路,相信工程师都非常容易理解与设计。然而时钟频率电路,由于不同的开发项目功能需求不一样,设计的方案选择也不尽相同,很难得到有效的统一设计。

STC12C2052AD单片机控制的数码管时钟,数码管是共阳4位时钟数码管,由于使用单片机真驱,电路比较简单,且使用的材料和工具也很简单,用数码管显示,单片机控制,两个按键调时,蜂鸣器整点报时。所需要的元件如下: 材料有以下这些: STC12C2052AD单片机一片 黄色共阳4位时

电源模块反馈电路错误,r15接入反馈电源到r14在到5号管脚。2.晶振布局布线错误3.typec差分对内误差控制5mil以内,尽量避免出现不耦合4.TF卡所有信号线要整组 ,做等长处理以时钟线为目标,目标控制在300mil以内。

扫码关注

扫码关注