- 全部

- 默认排序

一个学习信号完整性的layout工程师在刚开始接触PCB设计时,使用的是Allegro软件。在进行第一个板子设计时就遇到了这个布局的问题。导入网表之后,发现有好多的模块是相同的。因为刚开始不知道Allegro有模块复用的功能,所以就一点一点

相同的模块怎么呈圆形摆放

如图,一个圆形的板子有32个相同的模块,导入网表之后,模块复用之后怎么像图中一样,按照等分圆的方式摆放,复制led那个呈圆形摆放我知道,但是这个是所有的元件已经导入。

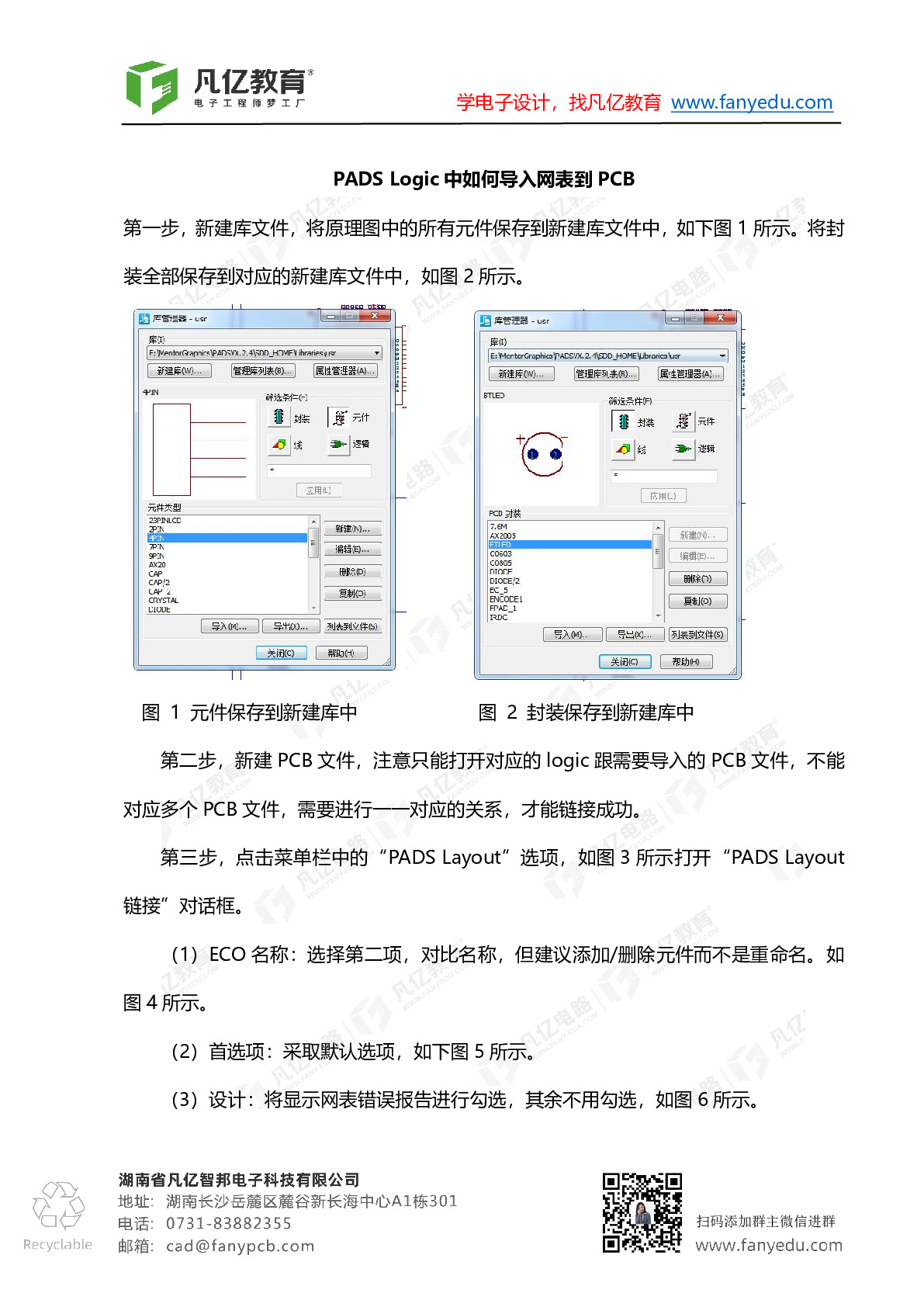

如何做好PCB设计的网表输入操作?网表输入操作是PCB设计前期的准备工作,而良好的网表输入能给PCB设计增上添花,间接提高设计效率,但很多电子小白更加重视PCB设计及加工,经常忽略网表输入,这是不正确的做法,我们来看看网表输入该如何做好?P

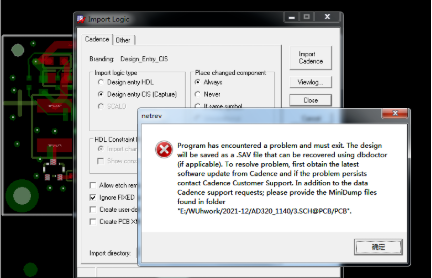

Allegro在导入网表文件时或者运行软件的时候出现如下截图报错,很多网友找不到解决方法,其实是可以根据下面俩种方法去解决这个问题的。第一种解决办法:1、当在设计过程中出现这个问题或者是在刚打开这个某一些文件出现这个问题的时候,可以点击菜单

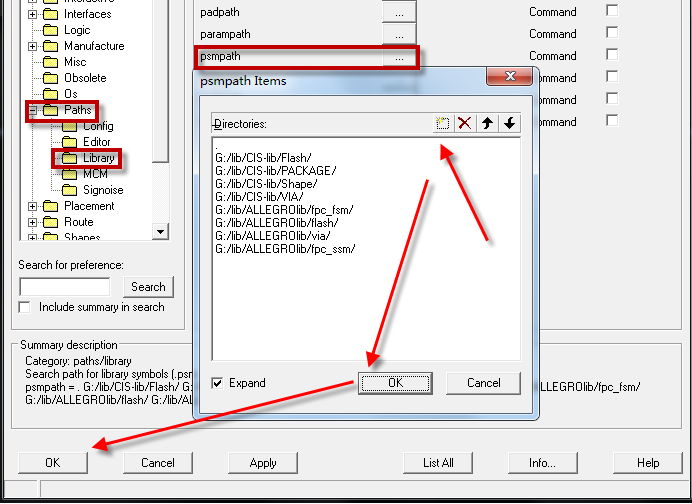

答:在将网表导入到PCB的过程中,经常会出现封装内管脚名或者数目与原理图内的器件管脚不一致,从而导致导入过程中报错,如图4-90所示: 图4-90 导入网表提示解析示意图上图是一个比较典型的封装中管脚与原理图中不一致而出现的报错内容。从上示报错内容(红色框标识的内容)可以获取以下信息点:Ø 器件的封装名为ERF8-40。Ø 封装中有几个多余的管脚,管脚名为41、42、43、44、45、46、47、48。Ø 封装中缺少了几个管脚,管脚名为H1、H

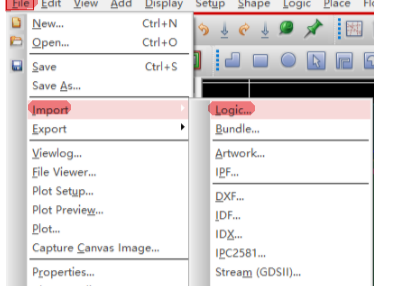

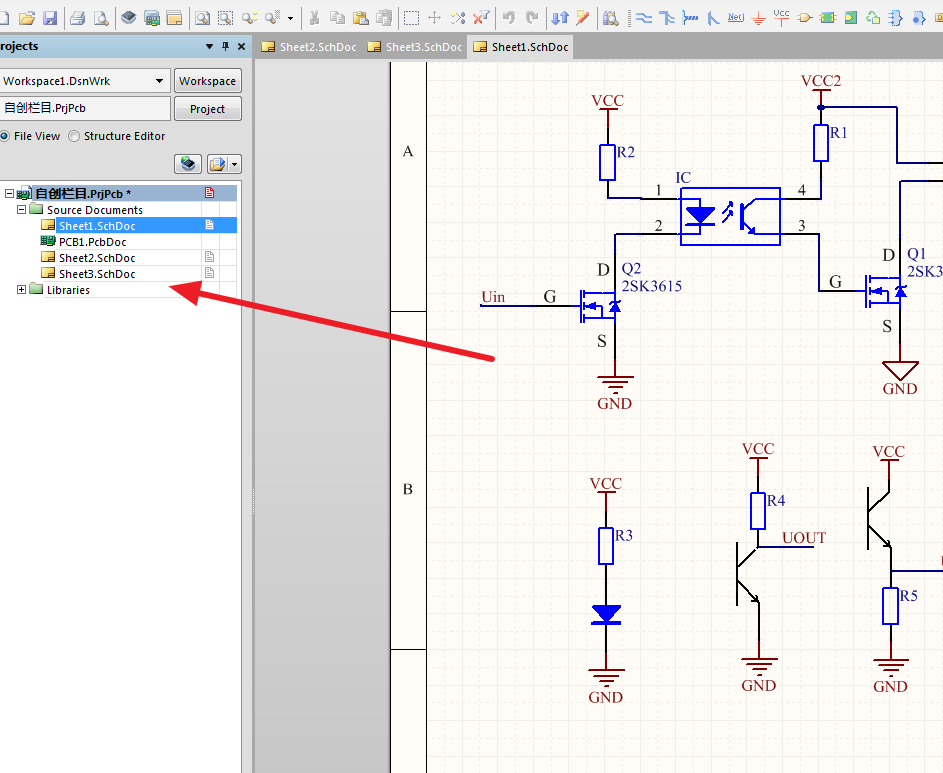

在AD的原理图绘制的时候我们想要只导入部分的原理图或者只导入单独一页的原理图如何进行操作。 这里目前有两种方式,第一种方式是直接放置屏蔽编译框,第二种就是进行网络比对的导入,就是我们使用导入网表比对的方法进行屏蔽部分原理图文件或者某些原理图。

扫码关注

扫码关注