- 全部

- 默认排序

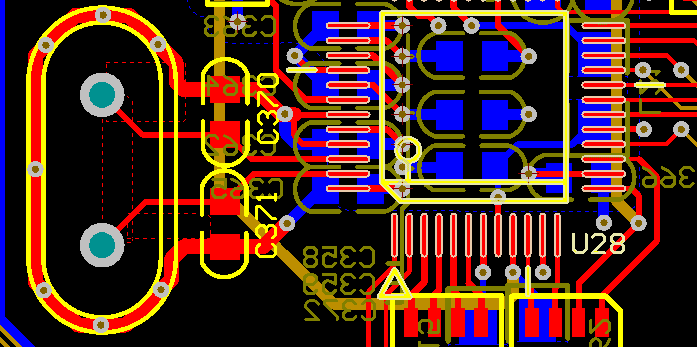

关于PCB设计中晶体晶振的布局和布线要求,布局要求:1、布局整体紧凑,一般放置在主控的同一侧,靠近主控IC。2、布局是尽量使电容分支要短(目的:减小寄生电容,)

在高速PCB设计中,寄生电感和噪声问题是常见的挑战,寄生电感是指电流在导体中产生的磁场所形成的电感,将影响信号的传输速度和稳定性,尤其是在高速PCB中更加明显,噪声问题也一样会对信号传输和系统性能产生负面影响。因此,在高速PCB设计中,需要

寄生电容在集成电路是无处不在,但若电路设计对电容敏感度低可忽略寄生电容带来的影响,但若电路设计要求芯片速度快或频率高,寄生电容将十分重要,所以若是遇见这个情况,该如何减小寄生电容带来的影响?首先需要知道的是,若模拟电路频率一旦超频率20MH

答:过孔的两个寄生参数是寄生电容和寄生电感。过孔本身存在着对地的寄生电容,如果已知过孔在铺地层上的隔离孔直径为D2,过孔焊盘的直径为D1,PCB板的厚度为T,板基材介电常数为ε,则过孔的寄生电容大小近似可以用以下公式来计算:C=1.41εTD1/(D2-D1)。过孔的寄生电容会给电路造成的主要影响是延长了信号的上升时间,降低了电路的速度。比如说,对于一块厚度为50Mil的PCB板,如果使用内径为10Mil,焊盘直径为20Mil的过孔,焊盘与地铺铜区的距离为32Mil,则我们可以通过上面的公式近似

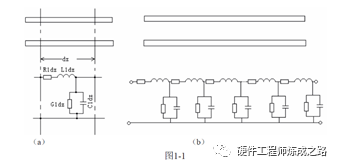

前几天写的关于示波器的文章,提到了探头上面的寄生电容,两个导体并排放置,天然就是一个电容。忽然想到,现如今HDMI 线里面的信号速率到上Ghz,HDMI线也做到了十几米,这么长,等效电容肯定不小啊?这怎么能传呢?信号不都被寄生电容滤波滤没了么?虽说这个时候也能用均匀传输线理论,集总参数模型,分布参数

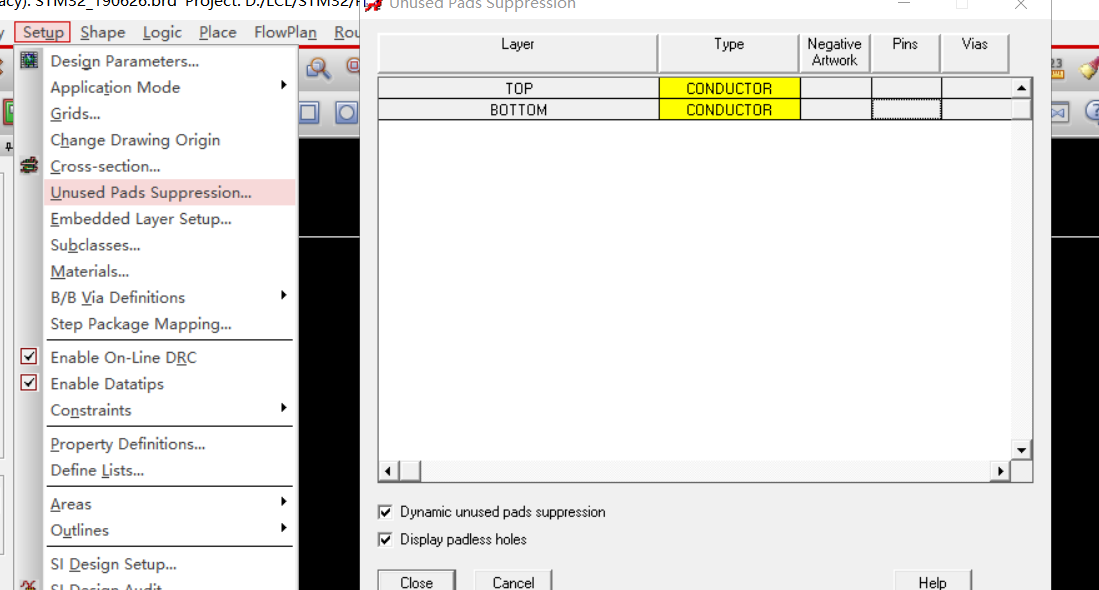

走线过孔与元器件通孔在内层的焊盘具有寄生电容的效应,易造成阻抗不连续,导致信号反射,从而影响信号完整性,allegro提供简单快捷的误判设计功能,可在设计端就将无走线连接层的焊盘去除,最大限度地保证过孔或通孔处与走线阻抗一致。

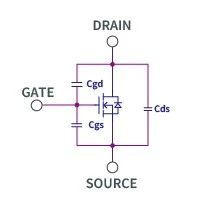

关于MOSFET的寄生容量和温度特性MOSFET的静电容量功率MOSFET在构造上,如图1存在寄生容量。功率MOSFET在构造上,如图1存在寄生容量 MOSFET的G (栅极) 端子和其他的电极间由氧化膜绝缘,DS (漏极、源极) 间形成PN接合,成为内置二极管构造。Cgs, Cgd容量根据氧化膜的

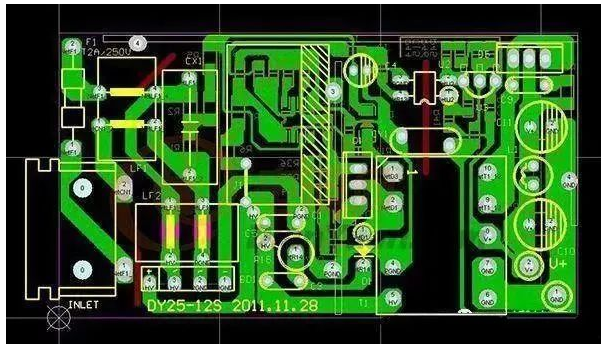

许多设计人员习惯于根据电路模型来思考系统行为。这些模型和电路图在某种程度上都是正确的,但是它们缺少一些确定系统行为的重要信息。电路图中缺少的信息是实际PCB布局的几何形状,它决定了系统中的元素如何相互电和磁耦合。那么,是什么导致真正的PCB

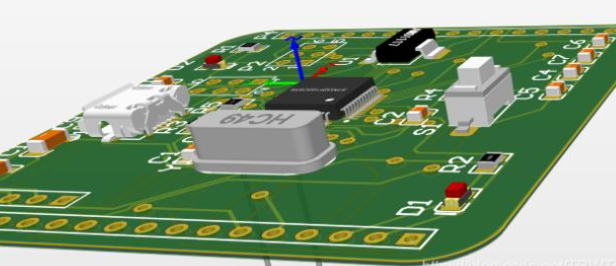

模块化电路设计有两方面的含义,其一是指电路设计功率器件的模块化,其二是指电源单元的模块化。我们常见的元器件器件模块,含有一单元、两单元、六单元直至七元,包括开关器件和与之反并联的续流二极管,实质上都属于“标准”功率模块(SPM)。近年,有些公司把开关器件的驱动保护电路也装到功率模块中去,构成了“智能化”功率模块(IPM),不但缩小了整机的体积,更方便了整机的电路设计制造。实际上,由于频率的不断提高,致使引线寄生电感、寄生电容的影响愈加严重,对器件造成更大的电应力(表现为过电压、过电流毛刺)。为了

扫码关注

扫码关注