- 全部

- 默认排序

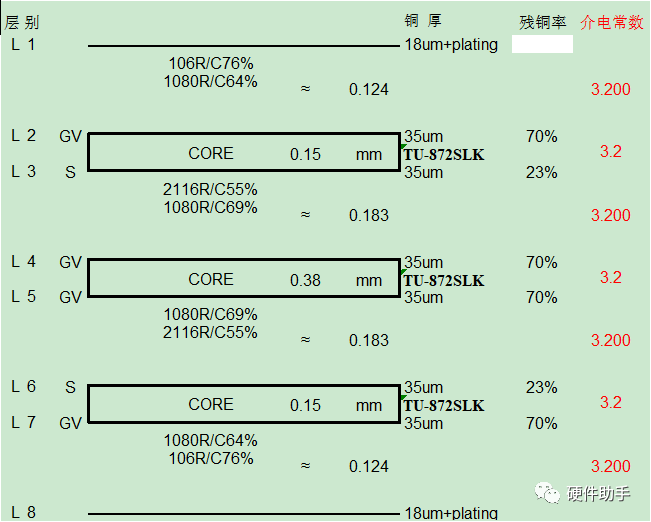

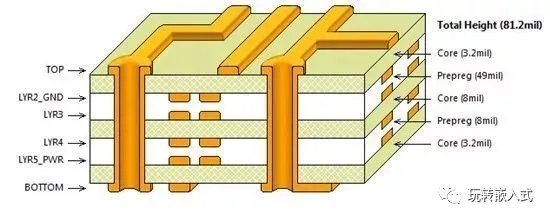

常见的一些叠层文件的形式多种多样,给出的方式也多样化,有的通过excel形式给出,有的通过制板说明文件给出,有的直接放在PCB设计文件中,通过Gerber文件给出。不管是哪种方式,其目的都是为了让设计人员有据可依,能设计出满足功能性能要求的PCB,让生产加工人员能制造出满足设计性能的PCB。 下面这种是将所有的信息都直接放在PCB设计中,并且生成Gerber文件一起提交到工厂。

1.多设备学习:手机、平板、电脑,学习更便捷,提升更高效 2.名师讲解:真实(置身课堂的真实感受)、 生动(授课形式更灵活、直观)、高清(悦目的视觉体验 3.全面教学资料:经典案例、常用封装库、设计工具、常见问题集、高手经验、常用规范

直播结束后,扫码添加助教领取课件直播时间11月25日 晚8点直播背景什么是阻抗?多层板应该怎么去叠?PCB走线应该走多粗?这些问题是不是很熟悉,这是很多工程师的老大难问题,其实这就是没有搞清楚叠层跟阻抗的问题。我们本次直播全面剖析多层板的叠层控制以及阻抗如何计算,教会大家轻松解决高速PCB设计中的阻抗与叠层。直播大纲1、什么是阻抗,为什么要控制阻抗?2、层叠的叠层原则是什么?3、如何理解PCB的参考层?4、4层/6层/8层常见层叠示例5、实例演示多层板叠层计算与阻抗计算直播内容案例图

本软件采用的软件讲解使用我们的Altium designer 19 ,主要讲解关于四层板常用的叠层,以及我们常用的叠层的设计的要素,设计叠层的一般参考的要点是那些,如何进行一个叠层的选用。

一般来说,影响PCB特性阻抗的因素:介质厚度H、铜的厚度T、走线的宽度W、走线的间距、叠层选取的材质的介电常数Er、阻焊的厚度。一般来说,介质厚度、线距越大阻抗值越大;介电常数、铜厚、线宽、阻焊厚度越大阻抗值越小。这些因素与特性阻抗的关系如图1-20所示。 图1-20 影响PCB特性阻抗分布图第一个:介质厚度,增加介质厚度可以提高阻抗,降低介质厚度可以减小阻抗;不同的半固化片有不同的胶含量与厚度。其压合后的厚度与压机的平整性、压板的程序有关;对所使用的任何一种板材,要取得其可生产的介质

★掌握PCB设计常用的设计技巧及熟悉PCB设计的整体流程★掌握DDR3设计的知识要点★掌握3W原则的PCB设计★了解T点拓扑结构及设计规则★掌握蛇形等长走线,阻碍线的使用★掌握叠层阻抗计算的方法★了解常见EMC的PCB处理方法

PCB的叠层设计在电子产品的开发中起到非常重要的作用,正确的叠层设计可明显提高信号完整性、降低电磁干扰,提升功耗效率等,然而PCB叠层设计并非那么容易好做,下面来看看想设计好PCB叠层该注意哪些方面?1、确定叠层层数在进行叠层设计前,先确定

在PCB的EMC设计考虑中,首先涉及的便是层的设置;单板的层数由电源、地的层数和信号层数组成;在产品的EMC设计中,除了元器件的选择和电路设计之外,良好的PCB设计也是一个非常重要的因素。

之前我们讲了PCB叠层7大设计技巧及注意事项方面,接下来我们将谈谈后面的知识点,希望对小伙伴们有所帮助,欲看前篇可点击右侧链接《PCB叠层怎么搞?这篇文一次性全告诉你!(上)》。8、控制信号和电源层的间隔为了避免信号层和电源层之间的互相干扰

扫码关注

扫码关注