- 全部

- 默认排序

CLASS就是类,同一属性的网络或元件或层或差分放置在一起构成了一个类别,即常说的类。网络类的就是把相同属性的网络放置在一起。如GND网络和电源网络放置在一起构成电源网络类。

"Reuse blocks"功能即“复用块”功能是Altium Designer 23设计环境中的一项强大工具,它允许用户将先前创建的设计模块存储在一个可访问的库中,并在需要时将其插入到新的设计中。通过"Reuse blocks",设计师可

前面介绍过模拟VCO是通过改变电容充放电电流的大小实现调频的,详见LLC闭环仿真之L6599 VCO建模与工作原理分析。那么数字环路该怎么实现呢?今天使用PSIM的C block分享一下。以前沿调制为例,如下图:每个中断周期内,软件通过环路

前面介绍过模拟VCO是通过改变电容充放电电流的大小实现调频的,详见LLC闭环仿真之L6599 VCO建模与工作原理分析。那么数字环路该怎么实现呢?今天使用PSIM的C block分享一下。以前沿调制为例,如下图:每个中断周期内,软件通过环路

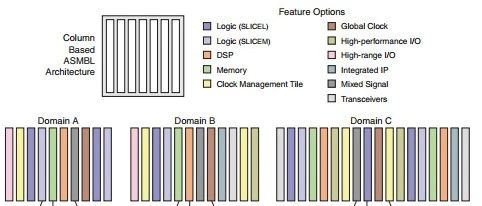

CLB是指可编程逻辑功能块(Configurable Logic blocks),顾名思义就是可编程的数字逻辑电路。CLB是FPGA内的三个基本逻辑单元。CLB的实际数量和特性会依器件的不同而不同,但是每个CLB都可配置,在Xilinx公司的FPGA器件中,CLB由2个 相

答:在使用Orcad软件进行原理图的过程中,会经常遇到这样的问题,原理图一共是绘制了很多页,但是在“Title block”的显示栏中,原理图页面的显示总是1 of 1,每次都要手动去进行修改,非常的麻烦,有没有什么方法进行调整下,可以让这个原理图的页面可以自动根据原理图绘制的情况,自信进行增加呢?下面,我们就对这个问题进行一一的解析,详细如下所示:第一步,选中原理图的根目录,DSN文件,然后执行菜单命令Tools-Annotate,进行参数的设置;第二步,进入参数设置界面之后,需要选择两个参数

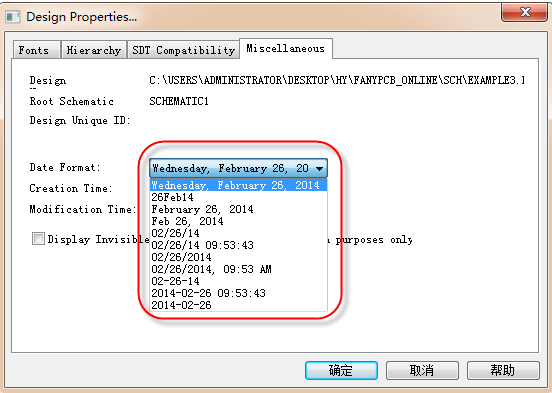

答:我们在使用Orcad软件进行原理图绘制的时候,新建原理图工程文件,默认在右下角都会出现Title block,做为每个个原理图的一个显示内容,在左下角都有一个当前的时间显示,当前默认的这个Title block的时间显示格式是,第一项是星期几,第二项是几月几日,第三项是年份,默认的格式都是这样的,我们对其进行修改的操作步骤如下所示:第一步,需要选中原理图根目录,执行菜单选项“Optiosn-Design Properties”,进行原理图设计属性的修改;第二步,进入设计属性之后呢,我们需要选

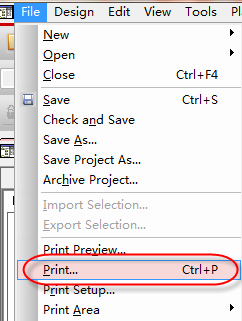

答:我们通过Orcad软件绘制完成原理图以后,会进行检查或者是发给别的工程师进行检查,这是需要将原理图文件打印成pdf文件,在打印的时候,我们发现一个问题,就是有时候输出的pdf的排序并不是按照我们原理图的排序,而是乱的。这时候就会有这样的一个疑问,我们输出的pdf文件的页码顺序是怎么决定的呢,应该怎么排,我们输出的pdf文件的页码顺序才是按照原理图的来的呢,下面我们就给大家介绍下:第一步,我们首先打开任意一份原理图,或者是新建的原理图,只要指定Title block的路径,在原理图的右下角都是

答:在设计原理图时,工程师们都喜欢在原理图中加上自己的独有标志或者是公司的logo,来表示这份原理图是该工程师绘制的或者是该公司的产品,这里我们就教一下大家,如何将公司的logo加入的原理图的Title block中,具体的操作如下:第一步,Title block是一个全局的变量,存在于每一页的原理图中,我们需要在库里面的Title block加入图片,然后更新到原理图中;第二步,在当前设计的库Design Cathe路径下找到Title block的库,复制到本地的库路径下,才可以对其进行更改

扫码关注

扫码关注