- 全部

- 默认排序

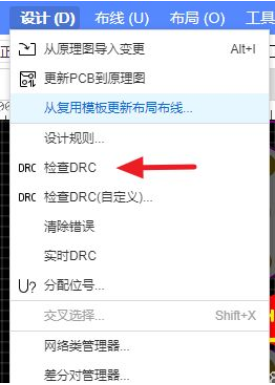

前期为了满足各项设计的要求,通常会设置很多约束规则,当一个PCB设计完成之后,通常要进行DRC。DRC就是检查设计是否满足所设置的规则。一个完整的PCB设计必须经过各项连接性规则检查,常见的检查包括开路及短路的检查,更加严格的还有差分对、阻

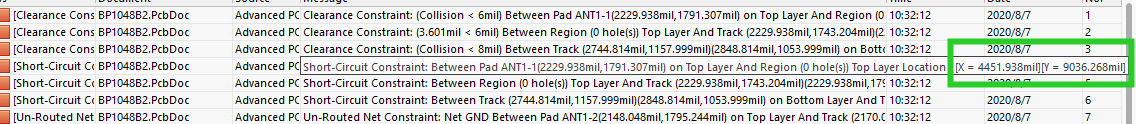

AD如何跳转到任意坐标?

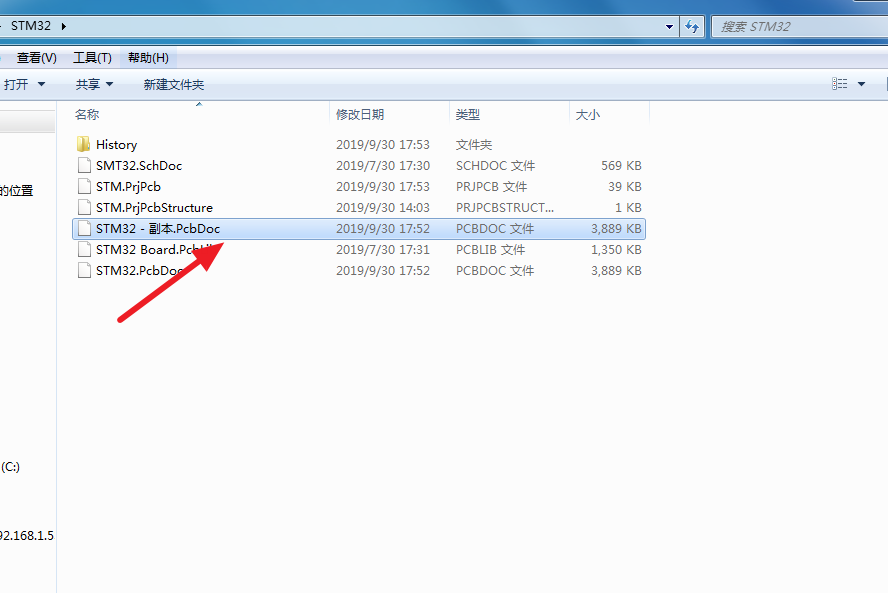

当我们进行DRC检查之后,在message的报告中显示出错误,如图所示,由于软件的某些原因,我们进行双击无法跳转到错误位置或者跳转的位置显示区域过大无法查看到具体错误,此时我们可以利用跳转至错误的坐标进行精准定位。

老师您好!我在给PCB增加内电层负片地的时候,存在死铜、岛铜无法去除的问题,在AD19上可以通过增加FILL消除DRC报错,在AD20里面这个方法无效,反复试验多次,最后只能缩小铺铜间距或者挪过孔的方法才可以消除;请问AD20里面有没有办法杜绝死铜产生?铺铜的时候可以勾选去死铜,但是负片里面没的选啊

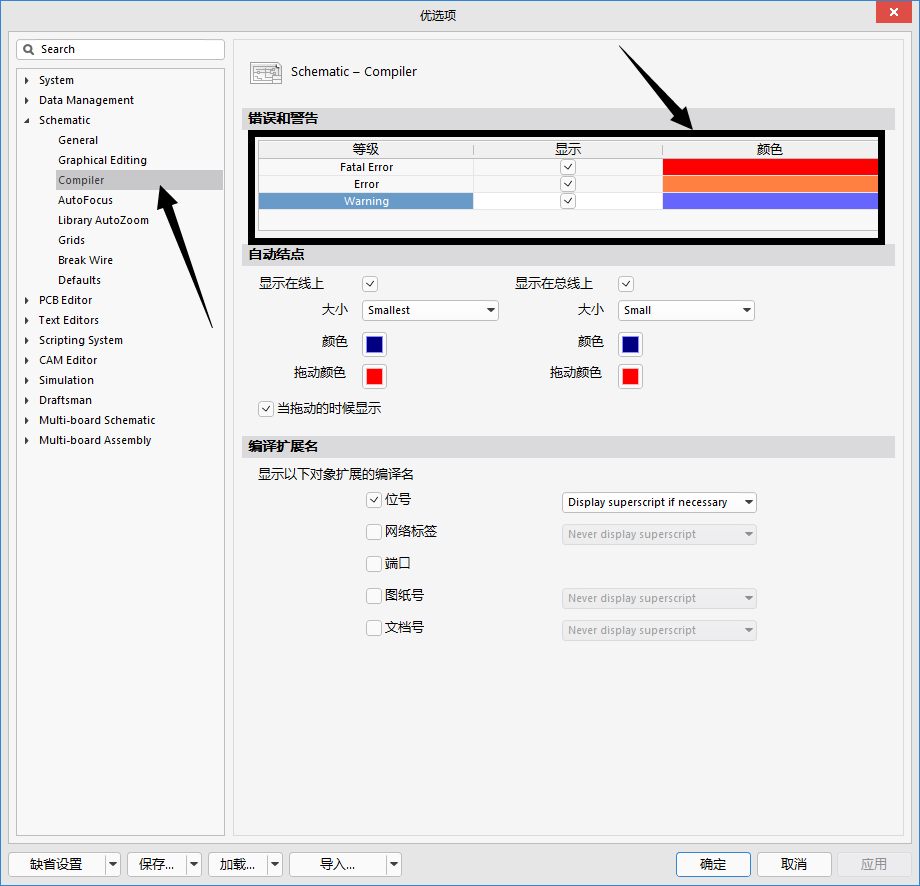

在我们设计完成原理图之后,设计PCB之前可以利用软件自带的ERC功能对于我们原理图去进行常规的一些电气性能的检查,避免出现一些常规的错误。

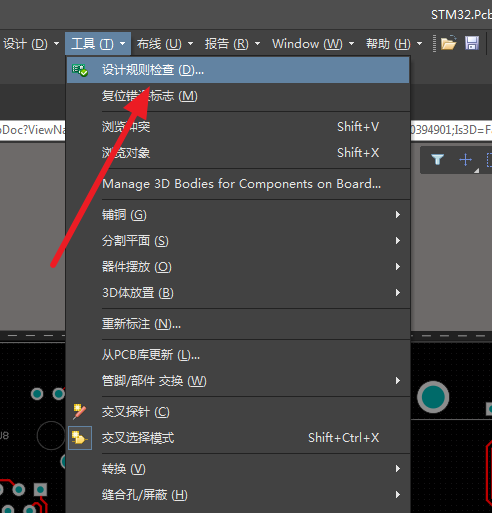

在设计PCB的时候,为了满足各项设计要求的原因,我们需要设置很多的约束规则,然后设计完成之后,去进行DRC检查。DRC检查就是检查我们的PCB设计是否满足所设置的规则,常见的DRC检查有开路,短路,间距等等规则约束。

我们在进行PCB设计时,在连线走线的时候,会经常出现这么两种情况:1.走线连接到焊盘上时,我们以为自己已经连接到了焊盘中心点上,早已连接上了,其实没有。那么,这个对于我们后期会造成虚焊,而且这一项有时DRC也检查不出来。所有为了减少我们不必要的损失,就来讲一下这项常用的方法。2.走线跟走线连接的时候,以为是连接上了,其实也是没有连接上来,会有开路的现象。

扫码关注

扫码关注