- 全部

- 默认排序

Short-Circuit C onstraint: Between Region (0 hole(s)) Bottom Layer And Pad IC1-25(555.046mil,964.177mil) on Bottom Layer Location:

PCB 进行design rule check 时报错,提示Un-Routed Net Constraint: Net V_VS Between Track (33.223mm,-13.425mm)(34.781mm,-13.425mm) on Bottom Layer And Pad R85-2(

答:使用Allegro软件进行PCB设计,一般会使用约束规则辅助设计,当设计时有对象违反了设置的约束规则,软件会以DRC标记的形式提醒设计者。

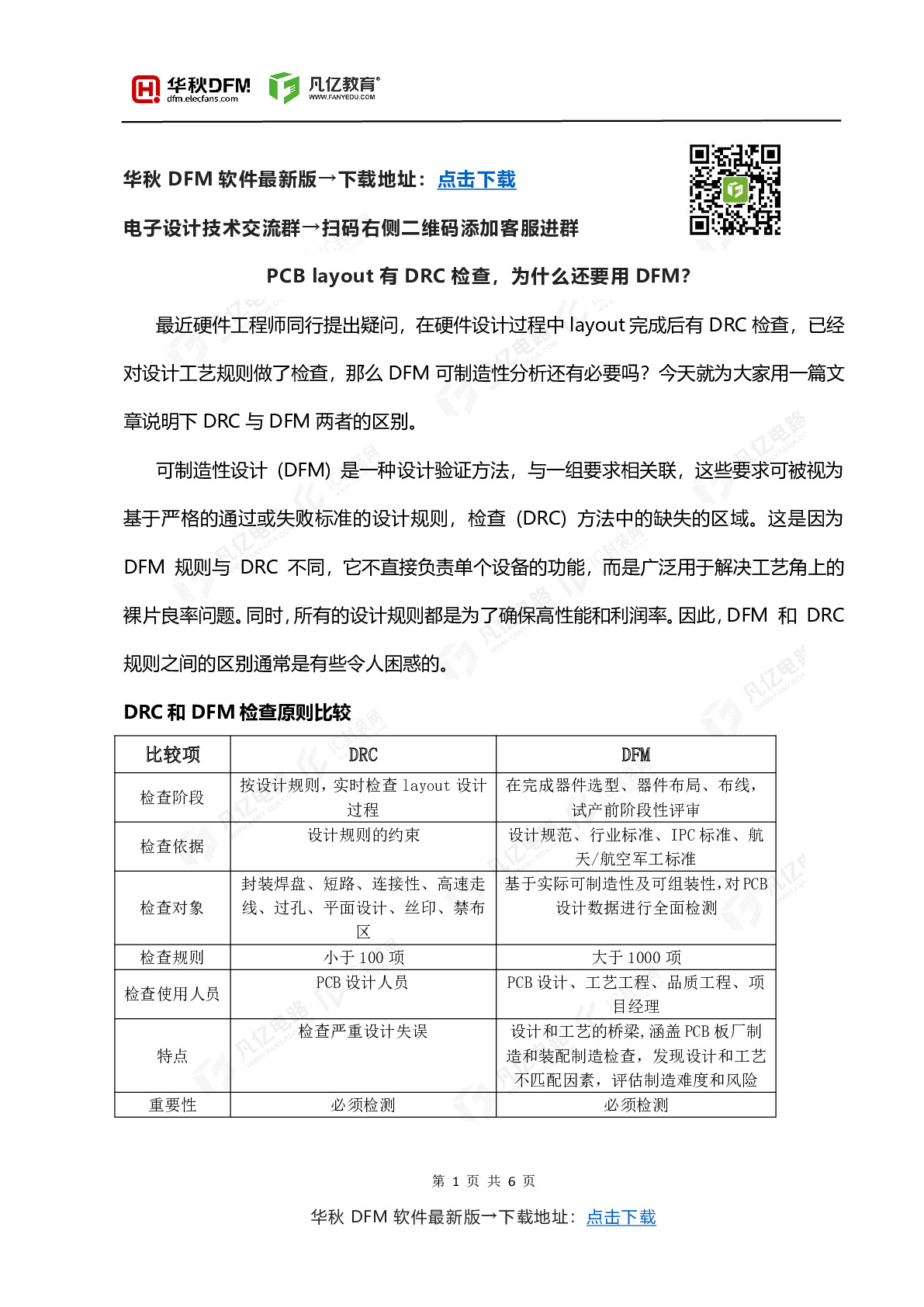

「雾林:请教一下,这个图形的报错怎么修改,不知道是不是跟封装有关系」 - - - - - - - - - - - - - - - 提示 short-circuit constraint

电流尽量从最后一个电容后面输出,自己调整一下铜皮宽度存在DRC报错3.此处铜皮宽度尽量加宽一些4.存在stub线头以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://i

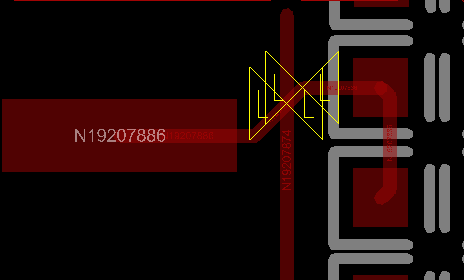

答:我们在PCB设计完成之后,都需要对整板铺地铜处理,然后在铺的地铜上面放置地过孔,但是有这样一个现象,相同的地过孔放重叠了,并不会产生DRC错误,我们应该如何设置,才可以让相同网络的重叠过孔产生DRC错误呢,这里讲解一下,具体操作如下所示:

PCB设计在连线走线的时候,会经常出现这么两种情况:1.走线连接到焊盘上时,以为已经连接到了焊盘中心点上,其实没有。那么,这个对于我们后期会造成虚焊,并且这一项有时DRC也检查不出来。所以为了减少我们不必要的损失,就需要去进行检查。2.走线跟走线连接的时候,本以为是连接上了,但是没有连接上来,会有开路的现象。

扫码关注

扫码关注