- 全部

- 默认排序

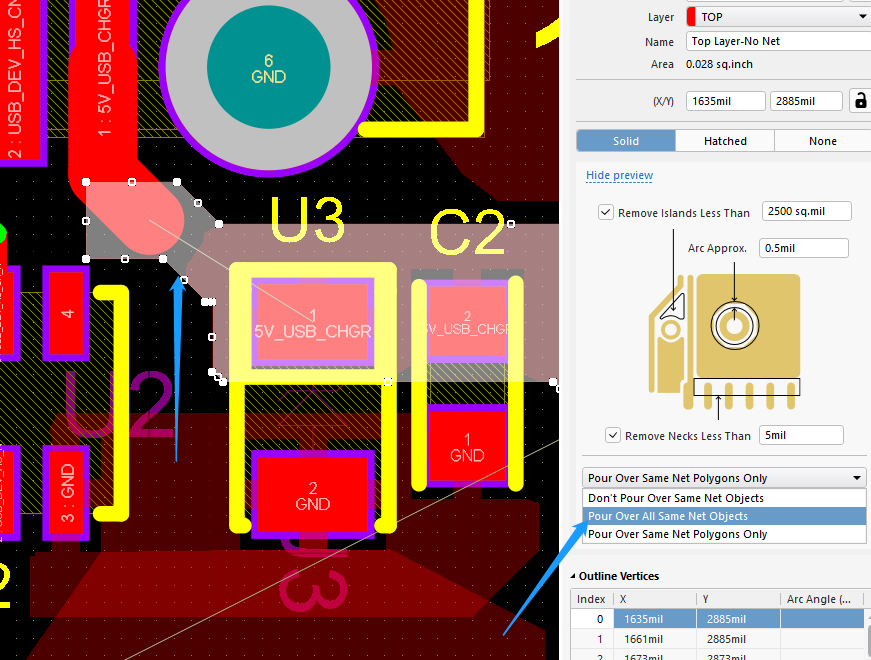

注意铺铜时要尽量把焊盘包裹起来,铜皮不要有任意角度,进行钝角2.电感挖空所在层需要右键重新铺铜进行挖空处理,焊盘处的铜皮不要进行挖空,否则存在开路3.电容先大后小排列摆放4.相同网络的铜皮和走线没有连接在一起,后期自己更改一下铜皮属性设置注

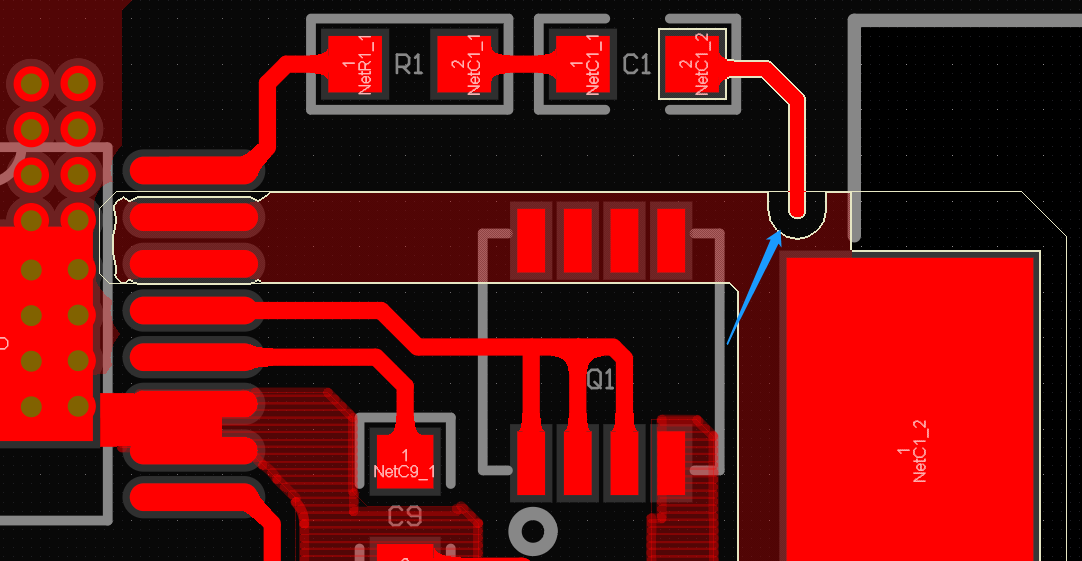

相同网络的铜皮没有连接在一起,后期自己修改一下铜皮设置,重启铺铜2.USB差分需要进行对内等长,误差5mil3.输入的过孔要打在电容的前面4.此处铜皮会出线载流瓶颈,自己在此处放置一块填充扩大载流路径5.输出过孔要打在最后一个电容的后面6.

相同网络的铜皮和走线没有连接在一起,后期自己调整一下铜皮属性重新铺铜2.走线未从焊盘中心出线,存在开路3.存在短路4.贴片器件焊盘需要放置top层,后期自己重新处理一下5.电感所在层的内部需要挖空处理6.pcb上存在多处DRC,后期自己更改

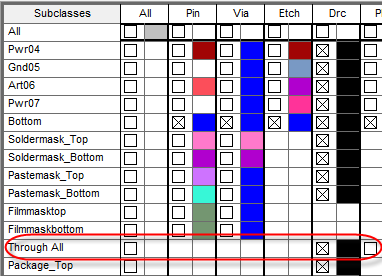

答:我们在PCB设计完成之后,都需要对整板铺地铜处理,然后在铺的地铜上面放置地过孔,但是有这样一个现象,相同的地过孔放重叠了,并不会产生DRC错误,我们应该如何设置,才可以让相同网络的重叠过孔产生DRC错误呢,这里讲解一下,具体操作如下所示:

电路中有许多网络NET, 然后我建立了class类来管理他们,我想对不同的类,设置不同的间距比如 VCC_1 类,我设置相同线直接的间距至少为1.524mm, 然后设置Vcc2类中相同类线的间距至少为1.08mm..点击确定,AD直接报错/ 这是怎么回事? 难道不可以对不同网络线中的相同网络设置不同的间距?

扫码关注

扫码关注