- 全部

- 默认排序

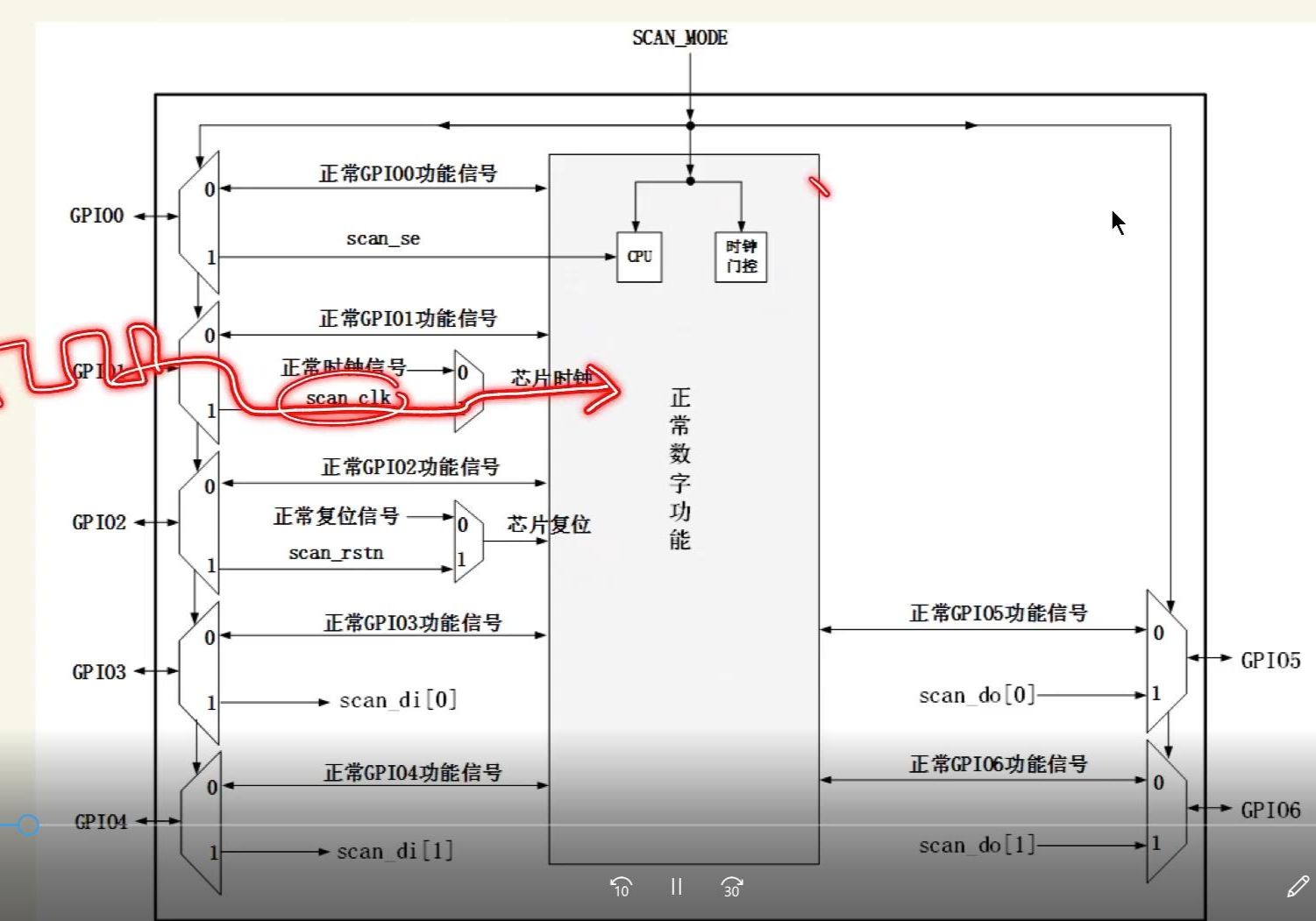

之前我们聊了可测性设计的四个常见问题及解决方法,接下来将更新下篇,希望能够帮助到小伙伴们,以及若是想看上篇,可点击右侧链接《可测性设计中常见问题及解决方法(上)》。5、有内部生成的异步复位、置位信号;内部生成的异步复位、置位信号的处理:有些

在IC设计中,可测性设计是很重要的内容,如果设计不当,将导致后续测试无法进行,或覆盖率降低,这两种都会大幅降低IC产品的竞争力,因此IC设计必须做好可测性设计,保证测试无误,下面就盘点可测性设计中遇见的问题及解决方法。1、设计中用到了时钟的

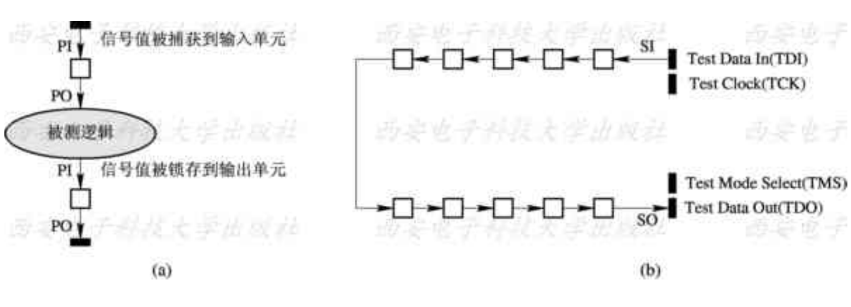

在IC设计阶段,为保证所设计的产品顺利上市,具有更高的竞争力,很多工程师会进行可测性设计确保无误,其中常用的方法莫过于基于JTAG的可测性设计,今天就给小伙伴们科普基于JTAG的可测性设计,希望能帮上忙。JTAG,也叫做边界扫描BSD,最初

扫码关注

扫码关注