- 全部

- 默认排序

Zemax 的STAR 模块能够将 FEA 数据包的热和结构变形数据直接导入到Zemax中,以分析对光学系统性能的影响。本文通过案例介绍如何在Zemax中载入热和结构变形数据,以及载入FEA数据后如何分析查看光学性能的变化。加载FEA数据相

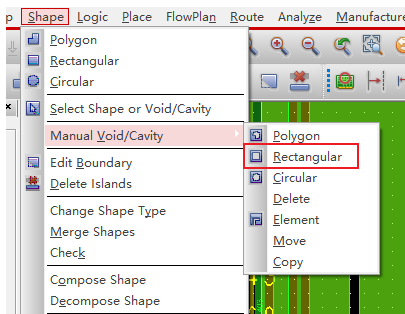

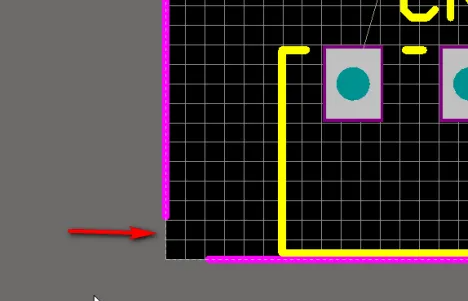

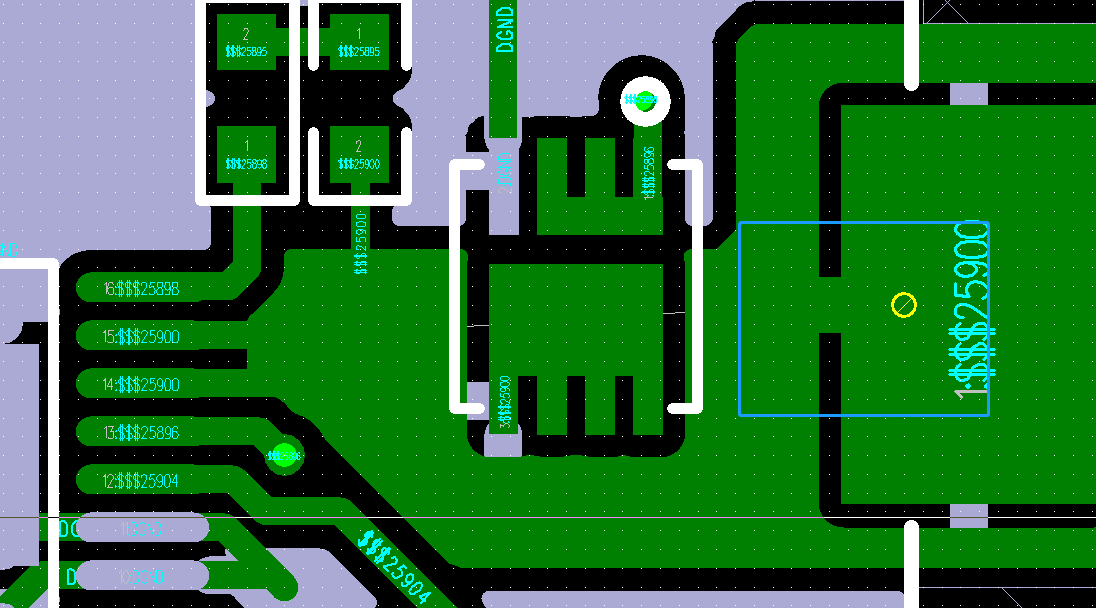

在PCB设计中,铜皮是电路板布局布线的重要载体,但有时候要根据项目需求对其进行切割或挖空,以此满足特定需求,那么如何操作?1、准备工作在进行切割/挖空操作前,先确保是否打开Allegro并加载器相关的PCB文件。2、Rectangular在

在PCB设计中,电子工程师需要进行大量的日常设计,会主动接触许多产品设计,以此提升技术及经验,其中之一是如何在PCB边框四角画出圆弧角?今天凡小亿开课谈谈如何使用AD实现这一步骤,希望对小伙伴们有所帮助。1、打开AD打开AD软件,加载其PC

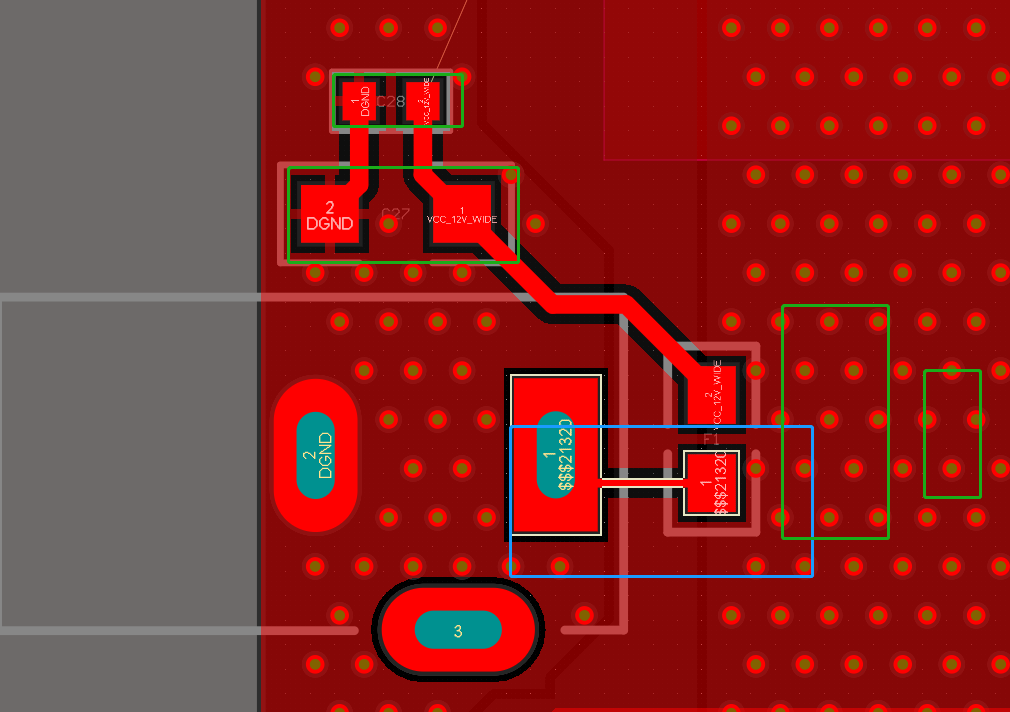

电源输出尽量铺铜处理,满足载流,输出电容靠近座子摆放2.采用十字连接可以在焊盘处添加一块铜皮增加载流其他的电感也是一样的处理3.电感所在层需要挖空处理4.芯片采用单点接地,输入和输出的地连接到芯片中间的散热焊盘上打孔进行回流,其他地方不用打

信号发生器是射频微波行业常用的测量工具之一然而很多小白都没接触过它,甚至不了解它,所以本文将详谈微波信号发生器的定义、特性、作用功能,为小白一一解惑。通常来说,信号发生器是产生不同频率、不同波形和不同幅度的电压和电流信号,并加载到被测器件或

此处可以添加一块填充增加载流2.电感所在层的内部需要挖空3.存在stub线头没什么大问题以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.co

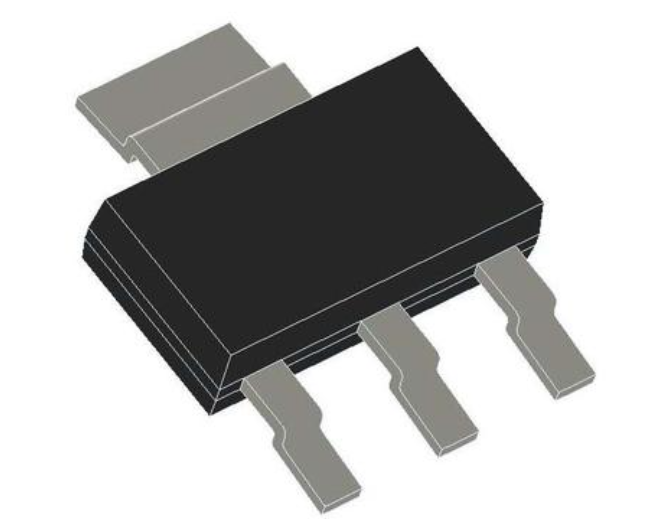

LDO应用要点

(1) VRF滤波由LDO的工作原理可知,Vref(基准电压)的稳定性与LDO输出电源的纹波及噪声密切相关。为了减小器件面积,某些LDO在片内不提供对VREF引脚的滤波。在这种情下,设计者需在VREF引脚附近添加10uF电容,以保证VREF的低噪声和低纹波(2) SENSE(感应)引脚的处理SENSE引脚是LDO、DCDC电源芯片上常见的引脚在PCB上,当电源输出端与负载端相距较远时,输出电源Vout需通过较长距离的PCB导线(或PCB铜皮)才能加载到负载上,由于负载电流流经

在加载license文件时显示Not connected to private license sever应该怎么办跪求各位老师解答 不胜感激

扫码关注

扫码关注