- 全部

- 默认排序

FanySkill集成了使用Allegro软件进行PCB设计时辅助设计人员提高工作效率的20多个Skill功能。包含了封装制作、PCB布局、PCB布线等PCB设计过程中大概率会使用到的功能。Skill大部分内容为网友共享的开源内容或共享的加密Skill,本工具的源码内容完全开放给广大使用者,可方便使用者进行Skill内容学习和Skill工具自主订制,学习者不仅可使用本 工具提高自身工作效率,亦可以DIY一套自己的Skill工具。

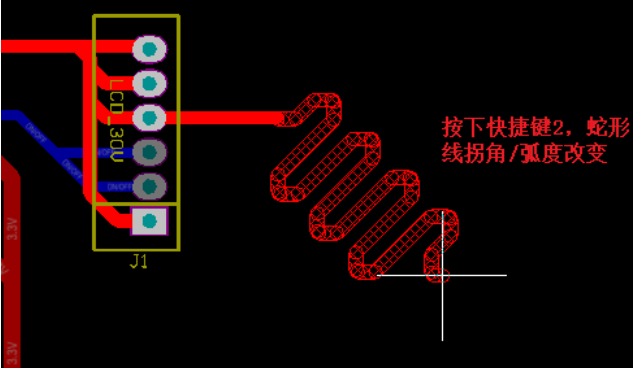

PADS蛇形等长处理

在做PCB设计时,为了满足某一组所有信号线的总长度满足在一个公差范围内,通常要使用蛇形走线将总长度较短的信号线绕到与组内最长的信号线长度公差范围内,这个用蛇形走线绕长信号线的处理过程,就是俗称的PCB信号等长处理。如图6-59示。图6-59

Altium Designer 21在之前版本的基础上对蛇形等长功能进行了优化,大大提高了设计的效率和规范性,具体改进可以参考以下说明。1.1新增两种等长样式 在之前的版本设计当中,等长设计时只有单一的U形等长。Altium Designe

PCB上的任何一条走线在通过高频信号的情况下都会对该信号造成时延时,蛇形走线的主要作用是补偿“同一组相关"信号线中延时较小的部分,这些部分通常是没有或比其它信号少通过另外的逻辑处理;最典型的就是时钟线,通常它不需经过任何其它逻辑处理,因而其延时会小于其它相关信号。

1. 掌握PCB设计常用的设计技巧及熟悉PCB设计的整体流程 2. 掌握DDR3设计的知识要点 3.掌握3W原则的PCB设计 . 了解菊花链拓扑结构及设计规则 . 掌握蛇形等长走线

器件摆放干涉2.走线尽量不要从小器件中间穿3.数据线等长误差+-25mil,也就是50mil,后期自己重新设置一下4.地址线误差是+-50mil5.数据线等长存在误差报错地址线也存在同样的问题,后期自己绕一下蛇形等长6.数据线和地址线之间最

扫码关注

扫码关注