- 全部

- 默认排序

开关三极管的三种电路应用图原理-LED1为低电平时,Q1BE截止,LED灭,这里R3的作用是确保LED1在0V~低电平阈值时,通过分压确保Q1BE未到开启电压,设计的时候要保留R3。

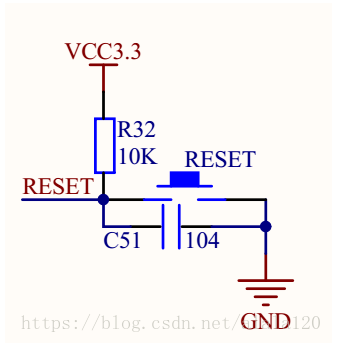

0组成:电源 复位 时钟 调试接口 启动1、电源 : 一般3.3V LDO供电 加多个0.01uf去耦电容2、复位:有三种复位方式:上电复位、手动复位、程序自动复位通常低电平复位:(51单片机高电平复位,电容电阻位置调换)上电复位,在上电瞬

三极管的正确用法

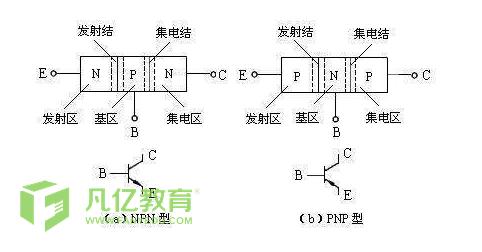

1. 三极管的基本特性:三极管是电流控制电流器件,用基极电流的变化控制集电极电流的变化。有NPN型三极管和PNP型三极管两种,符号如下: 2. 三极管的正确应用(1)NPN型三极管,适合射极接GND集电极接负载到VCC的情况。只要基极电压高于射极电压(此处为GND)0.7V,即发射结正偏(VBE为正),NPN型三极管即可开始导通。基极用高电平驱动NPN型三极管导通(低电平时不导通);基极除限流电阻外,更优的设计是,接下拉电阻10-20k到GN

MCU的I/o口,金黄线是低电平正常的。正常控制器使能。可是一旦控制器接入大一点的负载,控制器就是反复的开关。控制的是H桥。https://bbs.21ic.com/icview-3228782-1-1.html 陈老师,能否帮忙看看, 调试时有没有遇到类似的问题。

逻辑电路原理:与门逻辑电路和或门逻辑电路-若A,B,C端的高低电平分别为3V和0V。当A,B,C中有至少一个为低电平时(即0V),再加上二极管的导通压降可得,输出端F电压为0.7V,可以认为是低电平。

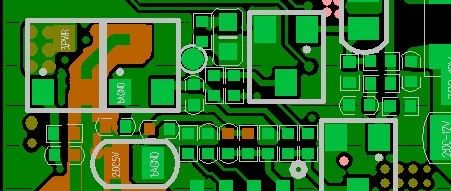

高速PCB设计指南之六

高速PCB设计指南之六第一篇 混合信号电路板的设计准则 模拟电路的工作依赖连续变化的电流和电压。数字电路的工作依赖在接收端根据预先定义的电压电平或门限对高电平或低电平的检测,它相当于判断逻辑状态的“真”或“假”。在数字电路的高电平和低电平之间,存在“灰色”区域,在此区域数字电路有时表现出模拟

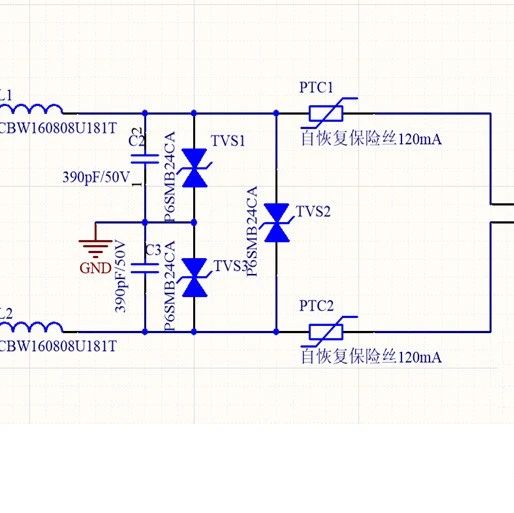

RS485电路原理图设计

RS485是差分信号,半双工、平衡传输线多点通信的标准,两个设备之间使用双绞屏蔽线缆连接,两个线缆分别传输A和B信号。RS485的传输速率与总线长度相关,最高可以达到10Mb/s,线缆越长,速率越慢;线缆越短,速率越快;RS485总线具有两种逻辑电平:高电平(1)和低电平(0)高电平(1):B线上的

一、单片机电路设计上拉电阻的选择大家可以看到电路设计中复位电路中电阻R1=10k时RST是高电平 ,而当R1=50时RST为低电平,很明显R1=10k时是错误的,单片机一直处在复位状态时根本无法工作。出现这样的原因是由于RST引脚内含三极管,即便在截止状态时也会有少量截止电流,当R取的非常大时,微弱的截止电流通过就产生了高电平。二、LED串联电阻的计算问题

答:orcad创建封装库时,放置管脚的Shape的含义是管脚的长度以及一些特殊含义,其表示的含义解释如下:Clock:时钟信号,管脚的长度是标准长度;Dot:低电平有效信号,管脚的长度是标准长度;Dot-Clock:低电平有效的时钟信号,管脚的长度是标准长度;Line:普通信号,管脚的长度是标准长度;Short:普通信号,管脚的长度比标准的长度要短一些;Short Clock:时钟信号,管脚的长度比标准的长度要短一些;Short Dot:低电平有效信号,管脚的长度比标准的长度要短一些;Short

扫码关注

扫码关注