- 全部

- 默认排序

降压芯片的选型和使用

降压芯片是在集成的电脑主机芯片,消费类电子产品的设计上面是经常是会被 使用到的,其优点在于,性能好,可以实现输入和输出的隔离,支持大电流的一个输出,但是纹波比较大,电路设计有点复杂,成本相对较高,但是对于高速电路中,选用DC/DC可以输出大电流,以及电容的配合,功耗的相对较低,是一个最佳的选择。

答:高速电路设计中电容的作用有如下几个:Ø 电荷缓冲池。电容的本质是储存电荷与释放电荷,当外界环境变化时,使得驱动器件的工作电压增加或者减少时,电容可以通过积累或者释放电荷来吸收这种变化,即将器件工作电压的变化转变为电容中电荷的变化,从而保持器件工作电压的稳定;Ø 高频噪声的重要泄放通路。高速运行的电路,时刻存在着状态的改变,这些改变将在电路上产生大量噪声干扰,我们需要将这些干扰泄放到相对稳定的地平面上,以免影响器件工作,因为电容在频率较高时表现为低阻抗,所以可以作为泄放通路

随着电路系统设计复杂性和集成度的大规模提高,电子系统设计所面临的的挑战不再以硬件工具为主,而是传输线的工作频率和信号完整性问题等,传统电路设计知识已无法应付,这也开始要求电子工程师必须具备高速电路设计知识,因为只有通过使用高速电路,才能实现

设计高速电路板的注意事项 怎样引起实际阻抗发生变化的,以及怎样用精确的现场解决工具(field solver)来预见这种现象。即使没有工艺的变化,其它因素也会引起实际阻抗很大的不同。在设计高速电路板时,自动化设计工具有时不能发现这种不很明显但却非常重要的问题。然而,只要在电路设计的早期步骤当中采取一些措施就可以避免这种问题。我把这种技术称做“防卫设计”(defensive design)。

答:高速电路设计中电容的作用有如下几个:电荷缓冲池。电容的本质是储存电荷与释放电荷,当外界环境变化时,使得驱动器件的工作电压增加或者减少时,电容可以通过积累或者释放电荷来吸收这种变化,即将器件工作电压的变化转变为电容中电荷的变化,从而保持器件工作电压的稳定;

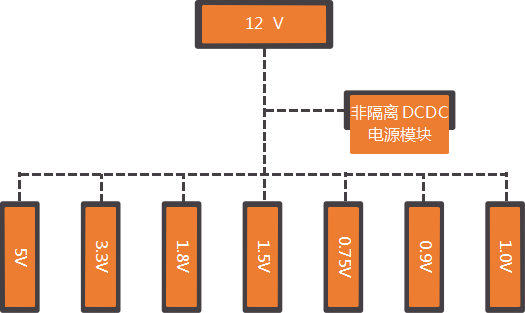

高速电路设计的电源架构

在高速电路设计中,一块单板往往有很多电源,常见的有5V,3.3V,2.5V,1.8V等,那么这么多种类的电源不可能直接通过背板从电源板获得。一般,单板只有一种或者两种输入电源,比如48V,10V等,再由它们产生单板上器件所需要的电源。那么,就单板怎么从12V(或者48V)生成5V,3V等电源,常见的有两种架构:1.集中式电源架构。2.分布式电源架构。(一)集中式电源架构集中式电源架构是最原始的电源分配架构,就是指系统由一个独立电源供电,并由这个这个独立电源直接变换得到我们单板所需要的各种电源。集

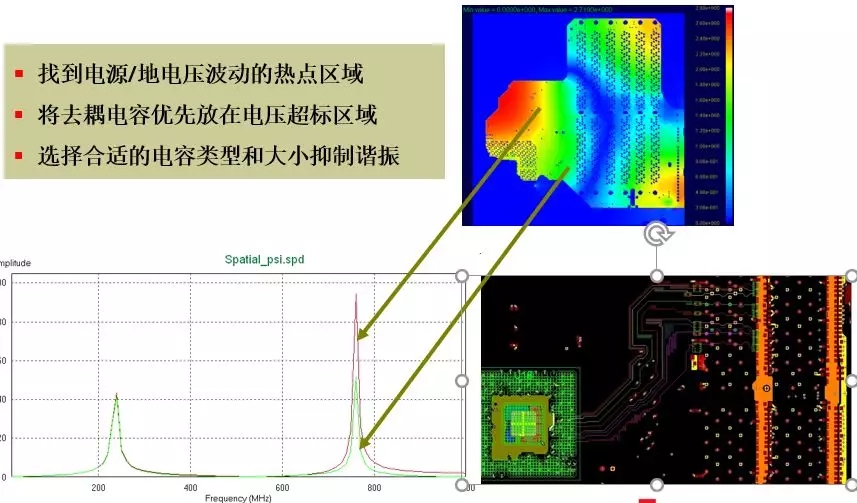

Sigrity PowerSI是IC封装和PCB设计快速准确的全波电磁场分析,作为专业的频域分析工具,为当前高速电路设计中面临的各种信号完整性(SI)、电源完整性(PI)和电磁兼容(EMI/EMC)分析提供快速准确的全波电磁场分析,并提供宽带 S参数提取以及频域仿真。PowerSI可以为IC封装和PCB设计提供快速准确的全波电磁场分析,从而解决高速电路设计中日益突出的各种PI和SI问题:如同步切换噪声(SSN)问题,电磁耦合问题,信号回流路径不连续问题,电源谐振问题,去耦电容放置不当问题以及电压

在高速电路设计中,链路中的每一个参数都有可能导致传递的信号出问题。今天就和大家分享一个平常大家不太注意的参数。 先回顾下在中学的时候,咱们学习的一个概念,趋肤效应:当信号的频率较越来越高时,信号都会趋向于导体的表面传递。这样就会导致信号流过导体的相对有效面积变小,从电阻的角度来分析,这就会导致电阻增加,导致传递能量的损失。 在电子产品使用的PCB,基本都是由铜箔和有机材料组成的 我们平时看到的铜箔,表面上看起来都是非常光滑的,实际上并不如你肉眼所见的那样,铜箔并不是完全光滑的。

判断一个信号是否为高速信号首先要区分几个误区。误区一:信号周期频率FCLOCK高的才属于高速电路设计其实我们在电路设计时考虑的最高频率往往取决于信号的有效频率(亦称转折频率)Fknee。 如上图信号周期频率与有效(转折)频率定义为:(实际中多数信号)误区二:电容、电感式理想器件在低速领域,电容、电感工作频段比较低,可以认为他们是理想器件。但在高速领域,PCB上的电容电感等已经不能简单的视为纯粹的电容电感了。例如:在低速领域电容我们可以视为断路,而在高速电路中,假设工作频率为F,则电容C

扫码关注

扫码关注

![高速电路设计实践_[王剑宇 著][电子工业出版社][2010][280页]](https://api.fanyedu.com/library/images/202211//4b1848df4813d5393acbff290364bd3b.png)