- 全部

- 默认排序

至于USB,SATA,PCIE等串行信号,并没有上述并行总线的时钟概念,其时钟是隐含在串行数据中的。数据发送方时钟包含在数据中发出,数据接收方通过接受到的数据恢复出时钟信号。这类串行总线没有上述并行总线等长布线的概念。但因为这些串行信号都采用差分信号,为了保证差分信号的信号质量,对差分信号对的布线一般会要求等长且按总线规范的要求进行阻抗匹配的控制

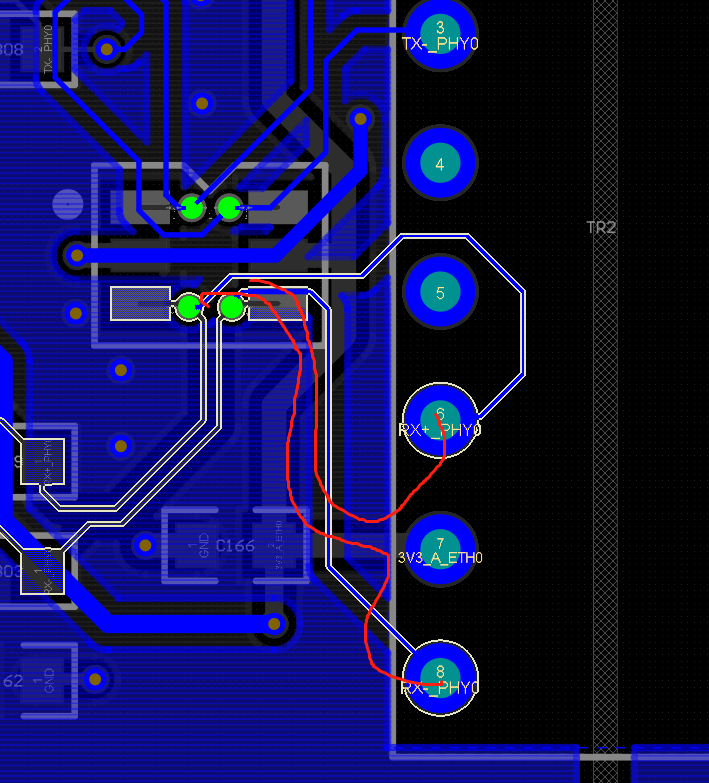

差分线要按阻抗线宽线距要求耦合走线网口到芯片的差分都需要优化,后期自己好好理解差分,然后走线需要调整一下2.器件摆放尽量中心对齐处理3.走线需要优化一下,不要有锐角4.TX分组错误5.注意等长蛇形走线尽量45度,不要直角6.除了散热过孔,其

PCB设计当中,为了满足时序匹配的要求,我们通常对数据总线进行等长,那么等长的时候,我们需要用到蛇形走线,那关于蛇形等长的参数设置及要求是怎么样的呢,我们又需要去学习呢?

你好 我现在在学AD蛇形走线,蛇形走完一根线。然后选中这根走线,在把它锁定。 请问如果选中?视频中老师用了快捷键。但是没说怎么选中的?请问如何快速选中?网上查了资料,没有找到。如何

全站最新内容推荐

- 1单口千兆以太网物理层收发器: YT8521SH-CA/YT8521SC-CA,PHY芯片、内置1.2V开关电源

- 2魏信+AD+第四次作业+千兆网口PCB设计作业评审

- 3全能22期- 莱布尼兹的手稿 第十一次作业 SFP

- 4VINKA 高抗干扰18按键触摸芯片/触控感应芯片VK3618I SSOP28/I2C输出功能

- 5工程师秘籍:Perberl转Gerber文件的注意事项

- 690天全能特训班22期AD-空沙-2DDR

- 7电磁兼容中EMI骚扰源特征

- 8USB3.0 HUB方案之VL813

- 990天全能特训班22期Allegro-莱布尼兹的手稿-SATA

- 10pads2.14软件120讲速成+2层实战项目视频教程

扫码关注

扫码关注