- 全部

- 默认排序

答:过孔的两个寄生参数是寄生电容和寄生电感。过孔本身存在着对地的寄生电容,如果已知过孔在铺地层上的隔离孔直径为D2,过孔焊盘的直径为D1,PCB板的厚度为T,板基材介电常数为ε,则过孔的寄生电容大小近似可以用以下公式来计算:C=1.41εTD1/(D2-D1)。过孔的寄生电容会给电路造成的主要影响是延长了信号的上升时间,降低了电路的速度。比如说,对于一块厚度为50Mil的PCB板,如果使用内径为10Mil,焊盘直径为20Mil的过孔,焊盘与地铺铜区的距离为32Mil,则我们可以通过上面的公式近似

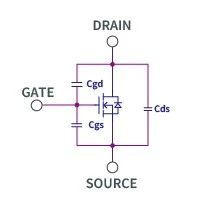

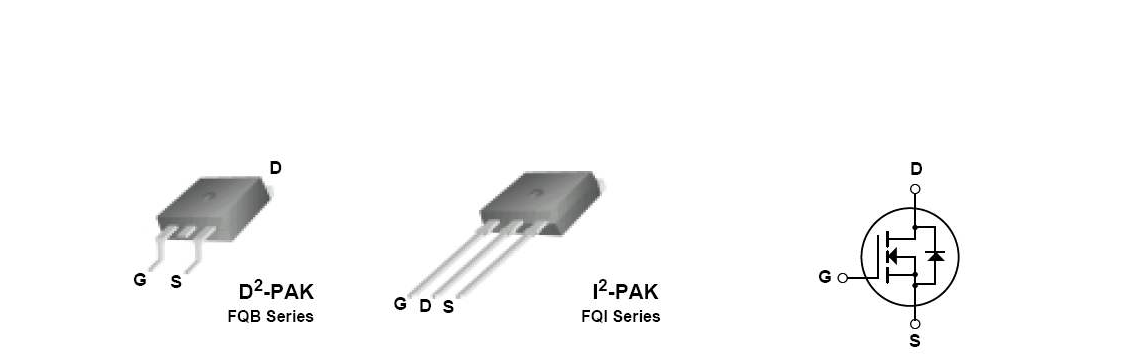

关于MOSFET的寄生容量和温度特性MOSFET的静电容量功率MOSFET在构造上,如图1存在寄生容量。功率MOSFET在构造上,如图1存在寄生容量 MOSFET的G (栅极) 端子和其他的电极间由氧化膜绝缘,DS (漏极、源极) 间形成PN接合,成为内置二极管构造。Cgs, Cgd容量根据氧化膜的

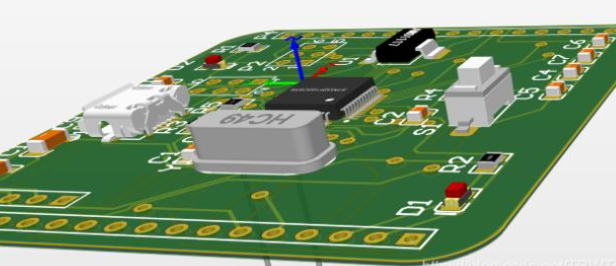

模块化电路设计有两方面的含义,其一是指电路设计功率器件的模块化,其二是指电源单元的模块化。我们常见的元器件器件模块,含有一单元、两单元、六单元直至七元,包括开关器件和与之反并联的续流二极管,实质上都属于“标准”功率模块(SPM)。近年,有些公司把开关器件的驱动保护电路也装到功率模块中去,构成了“智能化”功率模块(IPM),不但缩小了整机的体积,更方便了整机的电路设计制造。实际上,由于频率的不断提高,致使引线寄生电感、寄生电容的影响愈加严重,对器件造成更大的电应力(表现为过电压、过电流毛刺)。为了

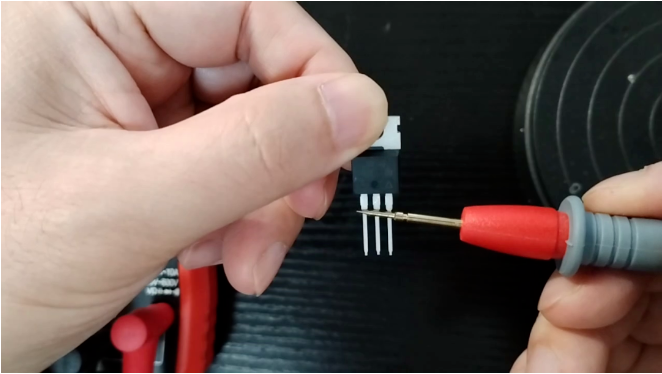

利用场管内部的寄生二极管的单向导通特性对场管的好坏进行判断。第一步 将三个脚进行短接放电这样做的目的对场管内部的寄生电容进行放电,防止有压差,使它内部产生导通,使得测量有误。第二步 测量内部二极管万用表打到二极管档,然后用两个表笔对这个 M

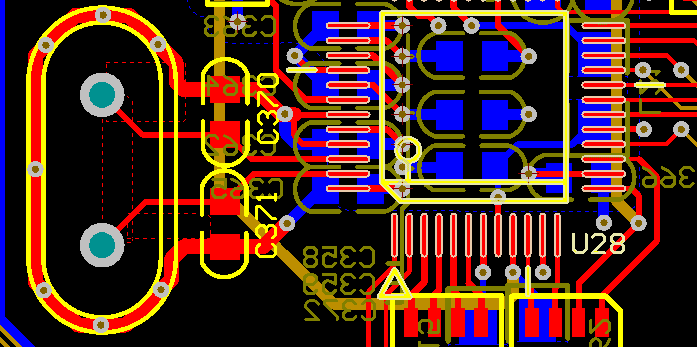

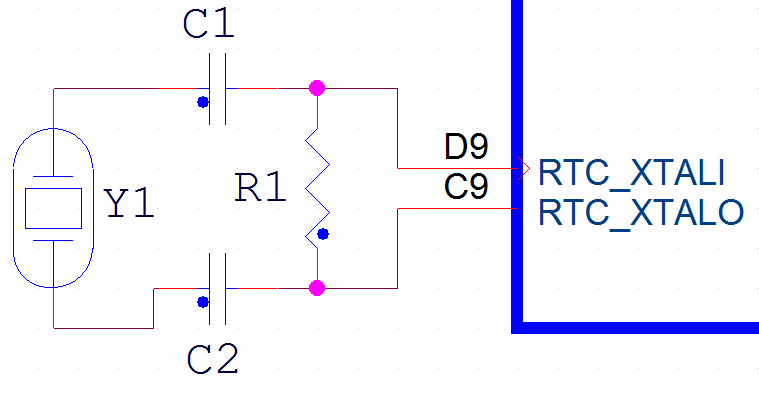

关于PCB设计中晶体晶振的布局和布线要求,布局要求:1、布局整体紧凑,一般放置在主控的同一侧,靠近主控IC。2、布局是尽量使电容分支要短(目的:减小寄生电容,)

寄生电容在集成电路是无处不在,但若电路设计对电容敏感度低可忽略寄生电容带来的影响,但若电路设计要求芯片速度快或频率高,寄生电容将十分重要,所以若是遇见这个情况,该如何减小寄生电容带来的影响?首先需要知道的是,若模拟电路频率一旦超频率20MH

PCB设计中晶体的π型滤波应该怎么设计?答:在晶体的电路设计中一般都采用π型滤波来进行设计,原理图设计部分如图1-41所示,后期我们在进行PCB布局布线的时候,要注意以下几点:布局整体紧凑,一般放置在主控的同一侧,靠近主控IC,尽量不要靠近板边;布局是尽量使电容分支要短,目的是为了减小寄生电容;晶振电路一般采用π型滤波形式,放置在晶振的前面;晶体和晶振的布局要注意远离大功率的元器件、散热器等发热的器件。其原理图设计部分如图1-41所示。 图1-41 晶体π型滤波电路示意图其PCB设计部

MOS管寄生电容

寄生电容是指电感,电阻,芯片引脚等在高频情况下表现出来的电容特性。实际上,一个电阻等效于一个电容,一个电感,一个电阻的串联,低频情况下表现不明显,而高频情况下,等效值会增大。在计算中我们要考虑进去。ESL就是等效电感,ESR就是等效电阻。不管是电阻,电容,电感,还是二极管,三极管,MOS管,还有IC,在高频情况下要考虑到等效电容值,电感值

许多设计人员习惯于根据电路模型来思考系统行为。这些模型和电路图在某种程度上都是正确的,但是它们缺少一些确定系统行为的重要信息。电路图中缺少的信息是实际PCB布局的几何形状,它决定了系统中的元素如何相互电和磁耦合。那么,是什么导致真正的PCB

全站最新内容推荐

- 1单口千兆以太网物理层收发器: YT8521SH-CA/YT8521SC-CA,PHY芯片、内置1.2V开关电源

- 2魏信+AD+第四次作业+千兆网口PCB设计作业评审

- 3全能22期- 莱布尼兹的手稿 第十一次作业 SFP

- 4VINKA 高抗干扰18按键触摸芯片/触控感应芯片VK3618I SSOP28/I2C输出功能

- 5工程师秘籍:Perberl转Gerber文件的注意事项

- 690天全能特训班22期AD-空沙-2DDR

- 7电磁兼容中EMI骚扰源特征

- 8USB3.0 HUB方案之VL813

- 990天全能特训班22期Allegro-莱布尼兹的手稿-SATA

- 10pads2.14软件120讲速成+2层实战项目视频教程

扫码关注

扫码关注