- 全部

- 默认排序

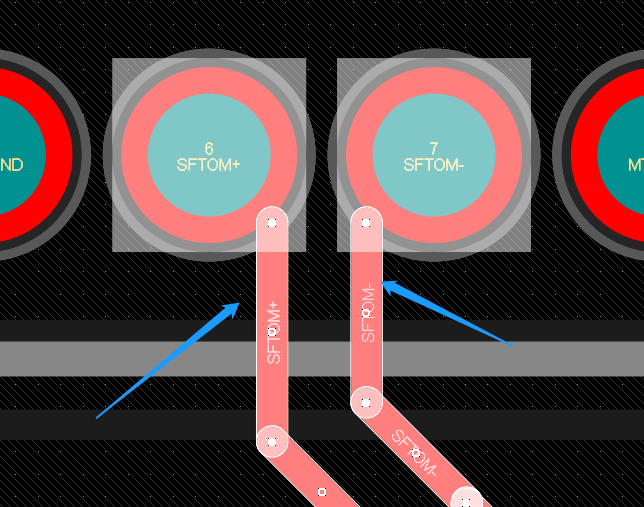

老师,按住shift拖动器件,复制出来的器件位号并没有加一,这个应该修改哪一个参数啊@凡亿技术组刘老师就像这样子

在SMT贴片加工时,芯片加工准确度将直接决定最终产品的质量,而工作人员在操作过程中可能遇见元器件偏移问题,如何针对这个问题采取预防措施,降低焊接不良影响?1、严格校准定位坐标定位坐标的准确性是确保元器件贴装位置正确的首要条件。在SMT加工时

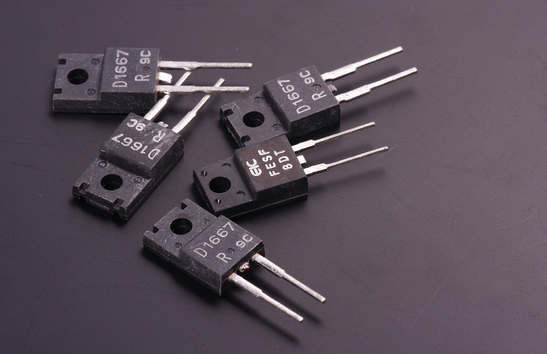

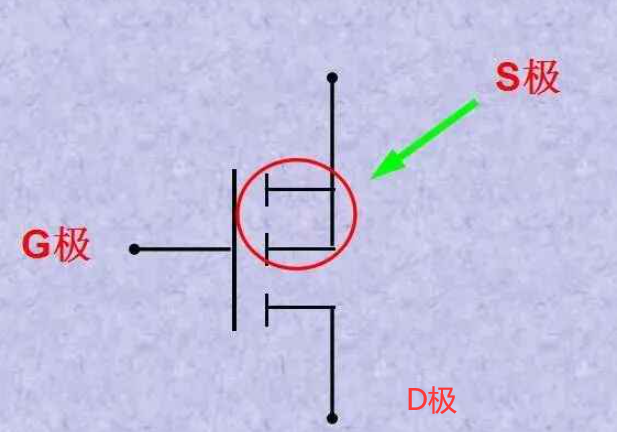

MOS管,即金属氧化物半导体场效应管,凭借着输入阻抗高、开关速度快、热稳定性优良等特点,是现代电子电路中常用的半导体器件之一。在MOS管的结构中有三个重要电极,分别是G极、S极、D极,下面聊聊这些电极。一般来说,一个典型的N沟道MOS管由一

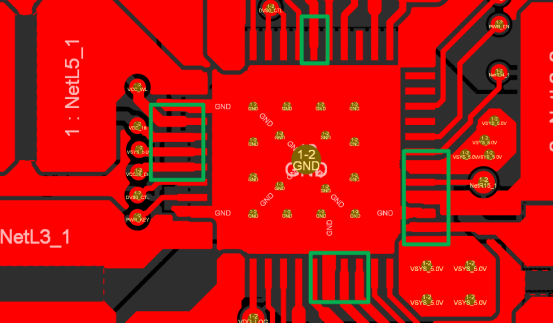

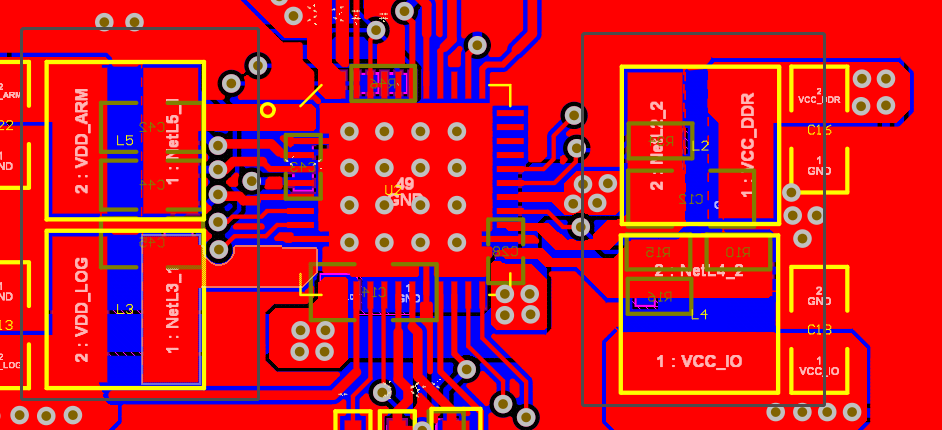

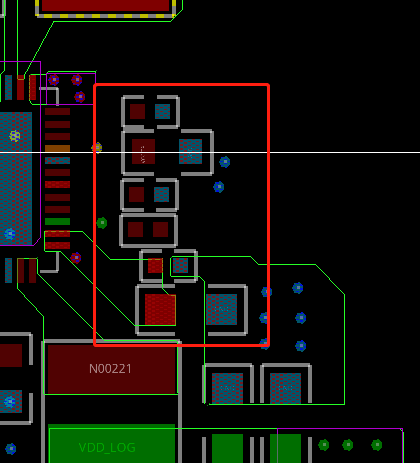

铺铜走线在焊盘内和焊盘保持宽度一致,出焊盘后再加宽 输出电源过孔打到最后一个电容后,靠经电容焊盘打孔 反馈信号走线加粗到10mil 此处铜皮过细长,应适当加宽铜皮 电感下方尽量不要摆放器件,和不要走线 器件中心对齐,器件丝印不要重叠 出芯片

电感底部不能放置器件,建议吧电阻电容放到IC底部去,重新布局下:铺铜尽量不要直角以及尖角:类似情况的都自己修改下。电感内部要挖干净:扇孔要对齐等间距:板上这种死铜去除掉:铜皮都仔细认真绘制,把焊盘包裹上,不要很随意:焊盘扇出主意拉直出去,跟

走线尽量从焊盘中心出线,避免造成开路2.差分出线要尽量耦合3.注意布局需要满足原理图规范4.注意确认此处是否满足载流5.电容尽量一个管脚一个,靠近摆放6.走线尽量不要从小器件中心穿,后期容易造成短路7.晶振尽量包地处理8.存在多处开路过孔不

注意布局的时候器件整体中心对齐:底层器件也注意对齐:打孔也需要对齐:5V电源走线加粗或者铺铜连接好:铺铜连接之后不需要再走线连接了:注意电感内部当前层需要挖空,放置一个keepout区域:过孔都没有对齐等间距:LDO电路的电源信号也需要加粗

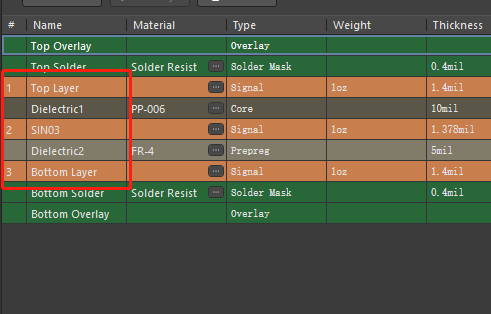

层叠一般都是双数,一般是4层,6层增加,高速信号都需要有完整的参考平面的2.差分走线注意要满足差分间距要求3.CC1和CC2属于重要信号管脚,走线需要加粗处理,ESD器件尽量靠近管脚摆放4.存在多处开路报错5.差分注意能顶层连通的就不用打孔

全站最新内容推荐

- 1单口千兆以太网物理层收发器: YT8521SH-CA/YT8521SC-CA,PHY芯片、内置1.2V开关电源

- 2魏信+AD+第四次作业+千兆网口PCB设计作业评审

- 3全能22期- 莱布尼兹的手稿 第十一次作业 SFP

- 4VINKA 高抗干扰18按键触摸芯片/触控感应芯片VK3618I SSOP28/I2C输出功能

- 5工程师秘籍:Perberl转Gerber文件的注意事项

- 690天全能特训班22期AD-空沙-2DDR

- 7电磁兼容中EMI骚扰源特征

- 8USB3.0 HUB方案之VL813

- 990天全能特训班22期Allegro-莱布尼兹的手稿-SATA

- 10pads2.14软件120讲速成+2层实战项目视频教程

扫码关注

扫码关注