- 全部

- 默认排序

PCB走线注意事项

FanySkill集成了使用Allegro软件进行PCB设计时辅助设计人员提高工作效率的20多个Skill功能。包含了封装制作、PCB布局、pcb布线等PCB设计过程中大概率会使用到的功能。Skill大部分内容为网友共享的开源内容或共享的加密Skill,本工具的源码内容完全开放给广大使用者,可方便使用者进行Skill内容学习和Skill工具自主订制,学习者不仅可使用本 工具提高自身工作效率,亦可以DIY一套自己的Skill工具。

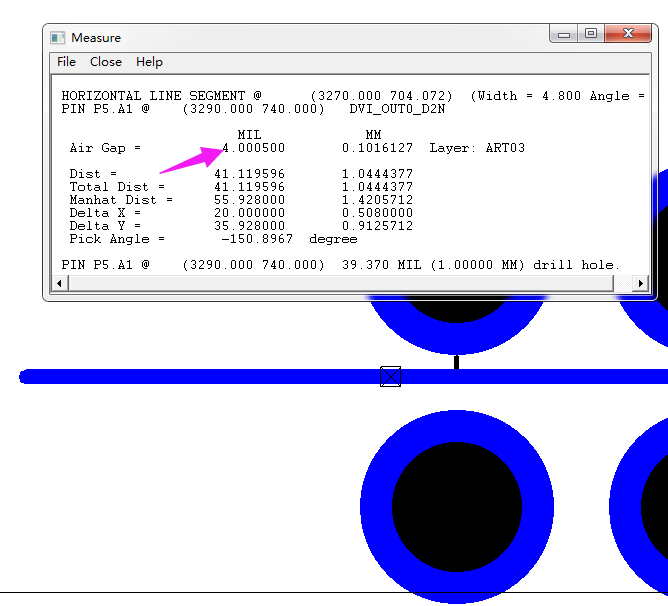

答:我们在pcb布线的时候,特别是走线在插件焊盘中间穿过的时候,我们尽量是让走线走在两个插件焊盘的中间,这样可以提高生产的可制造性。是手工使用slide命令去进行调整,很难调整到正中心,如图5-209所示,

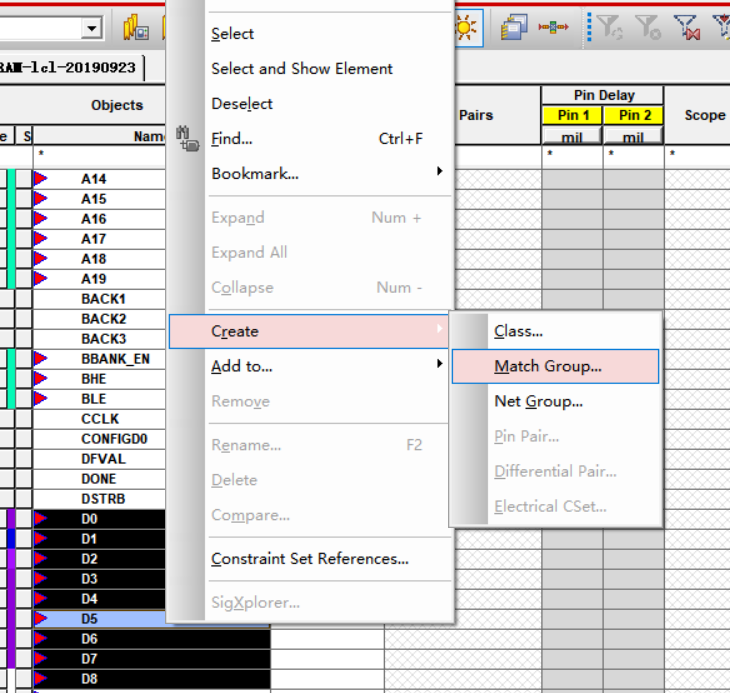

SDRAM信号线等长处理

在布线完成后,这里以SDRAM为例,要对SDRAM信号线进行等长处理,以满足时序要求。SDRAM的信号可分为数据线、地址线、控制线、时钟线,走线时要同组同层,间距满足3W原则,每组数据线的等长误差范围为+-50mil,地址线、控制线、时钟线的等长误差范围为+-100mil。

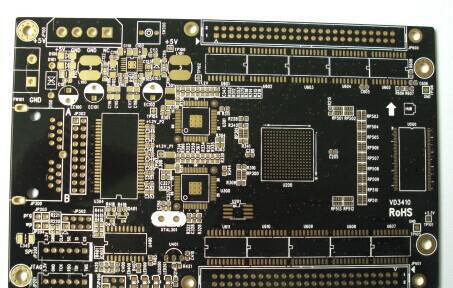

Altium Designerpcb布线规则,布板需要注意的点很多,但是基本上注意到了下面的这此规则,LAYOUT PCB应该会比较好,不管是高速还是低频电路,都基本如此。 1. Altium DesignerPCB设计一般规则 1.1 PCB板上预划分数字、模拟、DAA信号布线区域。

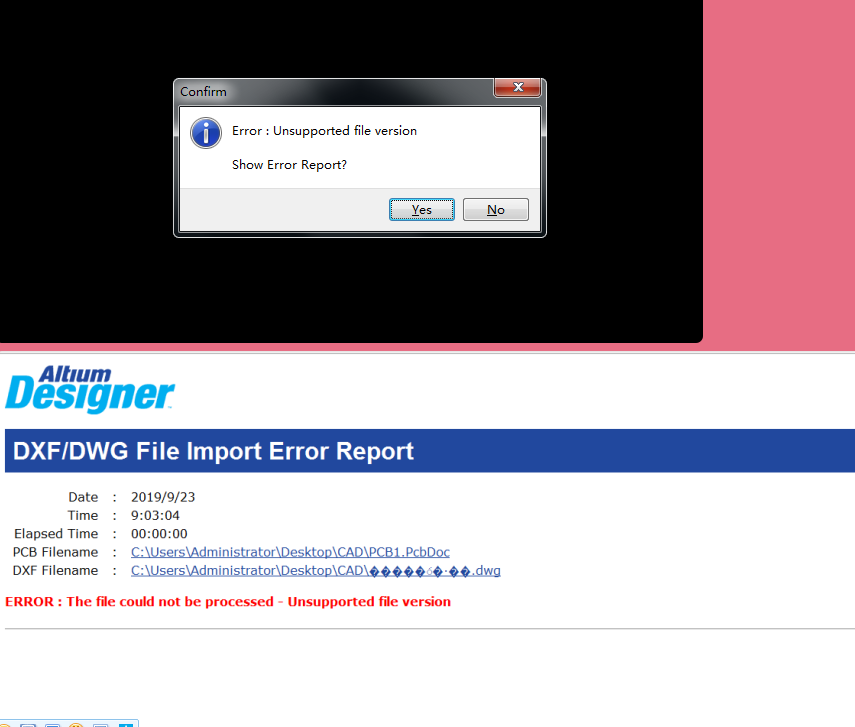

有很多消费类的板卡的结构都是异形的,都是由专业的CAD结构工程师对其进行精准的设计,pcb布线工程师可以根据提供的2D图,如DWG,DXP格式的,进行精准的导入操作,在PCB中定义板框结构。

答:我们PCB布局完成之后,需要对网络进行扇出,一般空的管脚、空的网络不需要进行扇出,为了提高布线效率,我们会对空的网络进行高亮显示,具体的操作步骤如下所示:

扫码关注

扫码关注